Friday, December 29, 2023

TSMC Set to Revolutionize Chip Technology with Trillion-Transistor Packages by 2030

Saturday, October 21, 2023

Intel Unveils Breakthrough 3D CFET Design at IEDM: Setting the Stage for Next-Gen Compact and Efficient Electronics

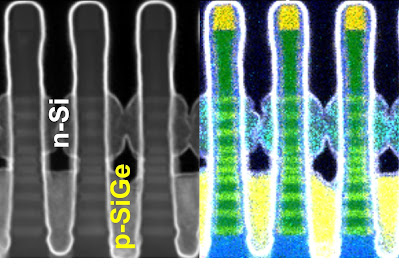

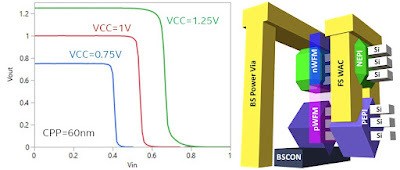

Intel researchers developed a 3D monolithic CFET device* with 3 n-FET nanoribbons atop 3 p-FET nanoribbons, separated by 30 nm gap. This industry-first device enabled the creation of functional inverters at a 60 nm gate pitch. Notably, it incorporated vertically stacked dual-Source/Drain epitaxy, dual metal work function gate stacks, and backside power delivery with direct device contacts. They also introduced a nanoribbon "depopulation" method for varying n-MOS/p-MOS device numbers. This research advances the understanding of CFET scalability for logic and SRAM applications and highlights key process enablers. The paper will be presented at the upcoming IEDM conference in San Francisco.

Comment: The stacked CMOS inverter at a 60 nm gate pitch represents an advancement in semiconductor design, allowing for denser circuits. The 60 nm distance between gates indicates a highly miniaturized design. Power vias provide vertical power connections to different layers, while direct backside device contacts enhance efficiency and heat dissipation. This development offers a glimpse into the future electronic devices being more compact, efficient, and high-performing than deploying "planar" designs in one layer like the FinFETs and GAA-FETs of today.

ALD plays a key role in manufacturing 3D monolithic CFET devices by assisting in crafting the architecture and providing atomically precise and even thin film layers at small scales. ALD ensures even coverage, which is important for 3D designs, especially on vertical areas and inside deep gaps. It's used to put down important materials in transistor gate stacks (High-k/Metal Gates or HKMG), as well as barrier and seed layers. ALD also helps in doping (SSD - solid state doping), which changes how semiconductors behave, and in creating spacers, important for separating and defining parts of transistors. In brief, ALD helps improve the CFET design and its overall performance.

* A 3D monolithic CFET device combines three-dimensional stacking and the Complementary Field-Effect Transistor (CFET) design within a single semiconductor structure. This approach vertically integrates both n-type and p-type transistors on the same substrate, promoting tighter integration and reduced interconnect delays. By leveraging the complementary operation of CFET and the benefits of 3D stacking, the device aims to enhance performance, miniaturization, and efficiency in semiconductor technology.

Wednesday, February 3, 2021

LIVE Stream - Advanced Process Technologies to Enable Future Devices and Scaling (invited), Rob Clark Tokyo Electron

Saturday, January 4, 2020

ASM International received TSMC’s Excellent Performance Award for ALD and Epitaxy products

The award was received by ASM in recognition of its technology collaboration with TSMC. During the presentation, TSMC explained three points that contributed to the award to ASM.

1) Outstanding development support.

2) Continuous efforts in productivity improvement.

3) Excellent delivery support on production ramp.

“On behalf of ASM and all of our employees, I thank TSMC for their recognition through this esteemed award,” said Chuck del Prado, CEO and President of ASM International. “Our partnership with TSMC is of strategic importance to ASM. We continuously focus on advancing our leading edge technology, including ALD and Epitaxy products and processes in support of our technology collaborations with TSMC."

ASM product portfolio for semiconducttor high volume manufacturing includes ewafer processing equipment for processes such as Atomic Layer Deposition (ALD), Plasma Enhanced ALD (PEALD), Epitaxy, Plasma Enhanced Chemical Vapor Deposition (PECVD), Low Pressure Chemical Vapor Deposition (LPCVD) and Oxidation/Diffusion. (source & credit www.asm.com)

Wednesday, June 19, 2019

TechInsights’ Logic, NAND, DRAM and Emerging Memory Process Roadmaps are here

TechInsights’ technology roadmaps show you the innovations we are monitoring

We constantly monitor the consumer electronics market to determine which manufacturers are planning to release new solutions, and when. We maintain and regularly update technology roadmaps in several different areas: Logic, NAND Flash Memory, DRAM, Emerging Memory, and Internet of Things Connectivity Systems on Chips, and more.

Updates to the roadmaps shown below are released throughout the year; check this page for updates.

Wednesday, May 8, 2019

4th CMC Conference Enabled Critical Information and Connections

Fab materials event in Albany, New York area April 25-26 featured GlobalFoundries keynote and Intel and TI presentations. Plan now for the 2020 April 23-24 event in Hillsboro, Oregon.

The event opened again, as in each of the prior three years, on an extremely strong business and technology keynote address by an executive from one of the CMC Fab member companies. The 2019 CMC Conference keynote was given by Dr. John Pellerin, Deputy CTO and VP of Worldwide R&D, GlobalFoundries. Pellerin talked about how demand for new high-volume manufacturing (HVM) semiconductor devices over the next few years will drive needs for increased numbers of new specialty materials as well as volumes of existing materials in his presentation on "Materials Challenges & Opportunities in Differentiated Technologies."

In the first session of the event covering global supply-chain issues of economics and regulations, G. Dan Hutcheson, CEO of VLSI Research, presented on "Slowdown: When did it start? What drove it? And When will the recovery come?" Hutcheson showed data from leading economic indicators that the recent decline in global semiconductor fab industry revenues due to memory chip prices may have already turned around.

TECHCET Sr. Analysts Dr. Jonas Sundqvist and Terry Francis presented updated information on demand drivers and forecasts for ALD/CVD precursors and Rare Earths, respectively. Sundqvist--also leader of the Thin Film Technologies Group at Fraunhofer IKTS--focused on how new 3D memory and logic chips demand more deposition precursors such that chemical volume growth will outpace that of silicon wafers, shown in the Figure. Francis showed how "Rare Earth" elements are not so rare at the elemental level, but complex dynamics between mining and refining and capitalism have led to a situation where mainland China currently controls most of the market for elements such as lanthanum (used in advanced ICs to create CMOS logic gates). Deep dives into all such materials matters are found in the TECHCET Critical Materials Reports (CMR), and you can find all of them online at https://techcet.com/shop/.

In addition to the annual spring CMC Conference in the US, there is also an annual fall CMC Seminar in Asia. The 2019 CMC Seminar will be held on October 17 in Taoyuan, Taiwan. For more information on CMC events see https://techcet.com/cmc-events/.

About CMC:

The Critical Materials Council (CMC) of Semiconductor Fabricators (CMCFabs.org) is a membership-based organization that works to anticipate and solve critical materials issues in a pre-competitive environment. The CMC is a business unit of TECHCET, and includes materials supplier Associate Members.

About TECHCET:

TECHCET CA LLC is an advisory services firm focused on process materials supply-chains, electronic materials business, and materials market analysis for the semiconductor, display, solar/PV, and LED industries. Since 2000, the company has been responsible for producing the SEMATECH Critical Material Reports™, covering silicon wafers, semiconductor gases, wet chemicals, CMP consumables, Photoresists, and ALD/CVD Precursors. For additional information about reports, market briefings, CMC membership, or custom consulting please contact info(at)cmcfabs(dot)org, +1-480-332-8336, or go to http://www.techcet.com or http://www.cmcfabs.org.

Friday, March 15, 2019

Samsung’s GAA Transistor, MBCFET™ aims at Reduced Size and Increased Performance

Source: Samsung LINK

Written by : Abhishekkumar Thakur and Jonas Sundqvist

Thursday, January 25, 2018

High Dielectric Constant Materials for Nanoscale Devices and Beyond

- The step coverage advantage of atomic layer deposition (ALD and is possible for, high‑k migration to FinFET CMOS technology.

- The use of high‑k on new semiconductor substrates such as III-V, Ge and 2D materials is currently being investigated and faces many challenges.

- The discovery of ferroelectric properties of HfO2 makes it viable for more potential applications.

High Dielectric Constant Materials for Nanoscale Devices and Beyond

Hiroshi Iwai, Akira Toriumi and Durga Misra

Electrochem. Soc. Interface Winter 2017 volume 26, issue 4, 77-81

Thursday, December 14, 2017

Globalfoundrfies to use quad patterning and Cobalt contacts for 7nm

Thursday, January 7, 2016

The Critical Materials Council to be managed by TECHCET in 2016

The organization has a new website at cmcfabs.org, which includes an overview of the Council’s mission, news of upcoming events and a Members Only portal for access to minutes of monthly phone/WebEx meetings and workshop details. The site also features access for Members to the TECHCET Critical Materials Reports and the related quarterly updates.

The next face-to-face meeting of CMC Fabs will take place May 3-6, 2016 in Hillsboro, Oregon. The meeting will include the annual CMC Materials Seminar held on May 5-6 that is open to the public. Sessions include a market briefing, supply chain issues and methods, the evolution of emerging materials in ALD / ALE, and the materials revolution around carbon. Speakers will be drawn from fabs, suppliers and analysts to address topics of concern and interest to the Council, and the semiconductor materials supply chain.

CMC Fabs is a unit of TECHCET CA LLC, a firm focused on Process Materials Supply Chains, Electronic Materials Technology, Materials Market Research and Consulting for the Semiconductor, Display, Solar/PV, and LED Industries. The company has been responsible for producing the SEMATECH Critical Material Reports since 2000.

Wednesday, September 2, 2015

TiC PEALD workfunction tuning by SK Hynix and KAIST

Temperature control for the gate workfunction engineering of TiC film by atomic layer deposition

Choong-Ki Kim, Hyun Jun Ahn, Jung Min Moon, Sukwon Lee, Dong-II Moon, Jeong Soo Park, Byung-Jin Cho, Yang-Kyu Choi, Seok-Hee Lee,The effects of the deposition temperature on titanium carbide film formed by atomic layer deposition are investigated for gate workfunction (WF) engineering. As the deposition temperature increases from 250 °C to 500 °C, the WF of the TiC decreases from 5.24 eV to 4.45 eV. This WF dependency on the deposition temperature is mainly attributed to the average WF of each orientation of the sub-planes of the TiC film. An investigation of a tunable WF is conducted through Auger electron spectroscopy, transmission electron microscopy, and X-ray diffraction.

Sunday, August 2, 2015

Improved gate oxide quality for PEALD TiN vs PVD TiN for FDSOI CMOS

- FDSOI transistors fabricated with either gate deposition process showed similar electrostatic performance.

- Gate dielectric quality metrics were significantly better when PE-ALD TiN was used compared to plasma sputtered TiN.

- A significant reduction in interface state density was inferred from capacitance-voltage measurements as well as a 1200× reduction in gate leakage current.

- A high-power magnetron plasma source produces a much higher energetic ion and vacuum ultra-violet (VUV) photon flux to the wafer compared to a low-power inductively coupled PEALD source.

Comparison of gate dielectric plasma damage from plasma-enhanced atomic layer deposited and magnetron sputtered TiN metal gates (OPEN ACCESS)

Monday, July 27, 2015

Hynix high bandwidth memory in an AMD Radeon ALD High-k Fury

Some facts from the reports:

- The GPU die has four Hynix HBM memory modules arranged around its perimeter.

- Both the GPU and the HBM modules are flip-chip bumped to a UMC fabbed interposer.

- The interposer is, in turn, bumped to a laminate substrate.

- The GPU itself is a massive measuring in at 23mm by 27mm large, and is believed to be fabricated using TSMC’s 28nm HKMG process.

Thursday, July 23, 2015

EUV, Atomic Layer Processes and KLA to solve all all Fab Issues at 7 nm and 5 nm

- Patterning and mask making - EUV, LER

- Fab flow and variation - CMP

- Selective processes - ALD, MLD, ALE

- Interconnects - RC

- Inspection and metrology - KLA

What Will 7nm And 5nm Look Like? - Delays at 10nm raise questions about what’s next.

Monday, July 13, 2015

GLOBALFOUNDRIES Launches Industry’s First 22nm FD-SOI Technology Platform in Dresden

Full story here: http://globalfoundries.com/newsroom/press-releases/2015/07/13/globalfoundries-launches-industry-s-first-22nm-fd-soi-technology-platform

Sunday, July 12, 2015

GLOBALFOUNDRIES Webinar: Extending Moore's Law with FD-SOI Technology

Only available by this link : https://www.youtube.com/watch?v=7VmQlpXKtHE#t=100

GlobalFoundries’ FD-SOI Revolution

Teepe offered, in broad strokes, GlobalFoundries' FD-SOI time schedule. While it was no formal announcement, his presentation implied the company’s oft-leaked but never confirmed big plans in FD-SOI.

Teepe came to Grenoble, ostensibly, to end the suspense.

He said, “We are developing 22nm FD-SOI process technology right now.” The plan is to qualify the process by early 2016 and start volume production by the end of 2016. Asked about what the company’s 22nm FD-SOI process entails, Teepe explained, “We are using STMicroelectronics’ 14nm FD-SOI in our frontend, while using 28nm FD-SOI in the backend.”

[...]

Thursday, July 9, 2015

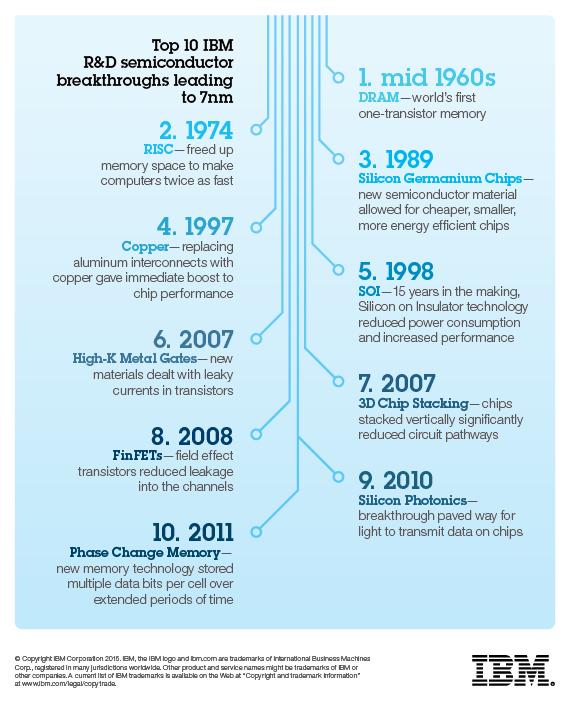

IBM present the first functional 7nm FinFET Test Wafer

Tuesday, July 7, 2015

Integration of Sub-10 nm ALD Gate Oxide on MoS2 with Ultra Low Leakage and Enhanced Mobility

Sunday, June 21, 2015

A Novel ALD SiBCN Low-k Spacer for FinFETs presented at VLSI 2015 in Kyoto

- SiBCN low k spacer was deposited in a batch furnace at 600 °C. The referral to low thermal process here may relate to earlier CVD processes at higher process temperatures.

- The process was run in thermal ALD mode with alternating layers of BN and SiCN.

- The B/C ratio in the film was controlled by adjusting the BN:SiCN cycle ratio

A Novel ALD SiBCN Low-k Spacer for Parasitic Capacitance Reduction in FinFETs

Thursday, June 18, 2015

Silicon Nanowire Remains Favorite to Replace FinFET

- Vertical or Lateral?

- With or without EUV?

- What Material?

%20(1).png)