Nanoimprint lithography (NIL) has emerged as a promising technique for the replication of intricate nano-scale features, offering higher resolution and uniformity compared to traditional photolithography methods. As semiconductor technology advances towards smaller and more complex structures, NIL holds the potential to revolutionize high-volume production processes. In this blog post, we'll delve into the current status of nanoimprint lithography and the possibilities it presents for future high-volume productions, as well as the main issues and concerns that need to be addressed.

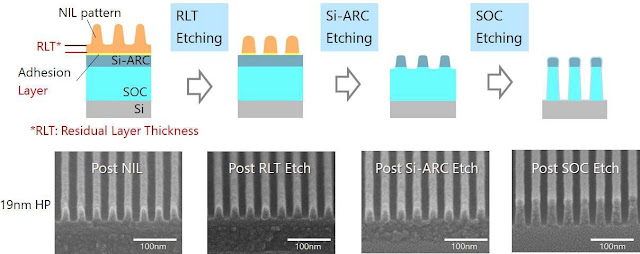

NIL utilizes a process where a patterned mask is brought into contact with a resist-coated substrate. The resist fills the relief patterns in the mask through capillary action, creating precise nano-scale features. With a focus on simplicity and cost-effectiveness, NIL doesn't require the complex optics found in traditional photolithography, making it an attractive option for semiconductor memory applications.

Early work on combining NIL and Atomic Layer Etching by AlixLabs Founders

AlixLabs (

www.alixlabs.com) founders and Lund Nano Lab (Lund University, Sweden) collaborated 2018 to exploit Atomic Layer Etching (ALE) for improved NIL quality and resolution. ALE involved Cl2 monoatomic layer adsorption on silicon, followed by controlled Cl2-modified silicon layer removal using argon bombardment. This precision process allowed diverse nanopatterns to be etched onto silicon wafers with electron beam lithography. The treated wafers served as robust nanoimprint stamps in a thermal process, transferring features as small as 30 nm into a poly(methyl methacrylate) layer. ALE's potential for ultrahigh-resolution nanoimprint stamp fabrication advances nanofabrication techniques significantly.

Most Recent Achievements:

Recent study by TEL and Canon have demonstrated NIL's resolution capabilities of better than 10 nm, positioning the technology as a candidate for printing multiple generations of critical memory levels using a single mask. The potential to eliminate material waste by applying resist only where necessary adds to its appeal. Moreover, the simplicity and compactness of NIL equipment allow for clustered setups, enhancing productivity.

NIL Addressing Challenges in DRAM Scaling:

Dynamic Random Access Memory (DRAM) memory faces the challenge of continued scaling, with roadmap targets aiming at half pitches of 14 nm and beyond. The complexities of achieving tighter overlays, greater precision in critical dimensions, and edge placement errors demand innovative solutions. In DRAM fabrication, overlay requirements are even more stringent than in NAND Flash, with an error budget of 15-20% of the minimum half pitch.

Edge Placement Error (EPE):

EPE, the difference between intended and printed features, poses a significant challenge in modern semiconductor manufacturing. The intricacies of multiple patterning schemes and intricate device layouts contribute to EPE's complexity. Ensuring accurate placement of features is critical for maintaining device yield and performance.

The Quasi-Atomic Layer Etch (Quasi-ALE) process

The process is a specialized etching technique employed in advanced semiconductor manufacturing, particularly in processes like Nanoimprint Lithography (NIL). Quasi-ALE combines elements of Atomic Layer Etching (ALE) and conventional etching methods to achieve precise and controlled material removal. In the context of Nanoimprint Lithography, Quasi-ALE is used to etch materials with exceptional precision, targeting nanoscale features while minimizing damage to the surrounding areas. It involves a cyclic process where alternating etching and passivation steps are applied to the substrate. Each cycle removes a controlled layer of material, ensuring highly uniform etching and minimal lateral etch. One can discribe Quasi-ALE as a more productive way of performing ALE.

The key steps of the Quasi-ALE process typically involve:

1. Etch Step: During this step, a reactive gas is introduced into the etch chamber, which chemically reacts with the material to be removed. This reaction results in the selective removal of the material layer.

2. Passivation Step: In this step, a passivating species is introduced, forming a protective layer on the substrate surface. This layer prevents further etching and preserves the material beneath.

3. Purge and Repeat: The chamber is purged to remove any excess gases, and the process is repeated in a cyclical manner. Each cycle removes a controlled atomic layer of material.

Quasi-ALE is particularly advantageous for applications requiring high precision and control, such as in Nanoimprint Lithography, where maintaining accurate pattern dimensions and minimizing damage is critical. By combining the benefits of both ALE and traditional etching, Quasi-ALE enables advanced semiconductor manufacturing processes to achieve unprecedented levels of accuracy and uniformity.

Addressing EPE with Nanoimprint Lithography:

Researchers are actively exploring techniques to mitigate edge placement errors in nanoimprint lithography. This includes focusing on overlay accuracy, critical dimension uniformity (CDU), and local CDU. Compensatory methods such as dose control and reverse tone pattern transfer are being investigated to improve CDU and minimize errors.

The Role of Dose Control:

Varying the exposure dose offers a means of achieving small shifts in critical dimensions. Initial studies suggest that dose variations could lead to CD shifts of one to 2 nm. This strategy holds promise for enhancing CDU in the imprint process.

Reverse Tone Pattern Transfer:

Reverse tone processes, involving spin-on hard mask (SOHM) application and etch-back, offer an alternative approach to pattern transfer. While this method provides advantages such as reduced resist erosion and improved wall angles, trade-offs between CDU and line width roughness (LWR) need to be addressed.

Looking Ahead: The Possibilities and Challenges:

While NIL exhibits impressive potential, there are key challenges to overcome before it can be effectively integrated into high-volume semiconductor manufacturing. Ensuring precise overlay accuracy, managing complex CDU requirements, and effectively addressing edge placement errors remain pivotal. As the industry strives to achieve the roadmap's aggressive scaling targets, the evolution of nanoimprint lithography will undoubtedly play a crucial role.

Nanoimprint lithography is poised to reshape the semiconductor manufacturing landscape, offering higher resolution and cost-efficiency compared to traditional methods. With ongoing research and development, addressing challenges such as overlay accuracy, CDU, and EPE, the path to successful high-volume production through NIL seems promising. As technology continues to advance, the journey towards perfecting nanoimprint lithography is an exciting one, holding the potential to shape the future of chip fabrication.

Tokyo Electron (TEL):

TEL specializes in Nanoimprint Lithography (NIL) technology, offering precision equipment, advanced etching solutions, and expertise in process control. They excel in alignment, overlay correction, CDU management, and etching technology.

TEL has previously demonstrated that for sub 7 nm CMOS technology, ALE and ALD integration improves SAC and patterning processes, achieving precise CD shrinking and enhanced selectivity.

Canon:

Canon contributes to Nanoimprint Lithography (NIL) advancement by leveraging TEL's strengths in alignment, overlay correction, CDU management, and advanced etching solutions. They integrate these capabilities with the Reverse Tone Pattern Transfer, ensuring precise pattern replication and fidelity. Canon's focus on innovation drives high-resolution, cost-effective solutions for semiconductor manufacturing.

Canon has introduced a groundbreaking solution in the field of semiconductor technology with the development of the world's first mass-production equipment called the "FPA-1200NZ2C." This innovative tool utilizes nanoimprint lithography, a cutting-edge technique that involves imprinting nanometer-scale mask patterns onto substrates. By adopting this novel approach, Canon aims to overcome the limitations of conventional miniaturization methods. The FPA-1200NZ2C is already in use by Toshiba Memory, a prominent semiconductor memory manufacturer. This advancement marks a significant step forward in semiconductor manufacturing, enabling the creation of more intricate and advanced circuit patterns.

Sources:

High-Definition Nanoimprint Stamp Fabrication by Atomic Layer Etching — Lund University

Nanoimprint post processing techniques to address edge placement error (spiedigitallibrary.org)

Nanoimprint Lithography | Canon Global

FPD Lithography Equipment | Canon Global

Benefits of atomic-level processing by quasi-ALE and ALD technique - IOPscience

www.alixlabs.com

Acknowledgement :

Thanks for sharing the SPIE article on LinkedIn and giving insights Frederick Chen!

%20(1).png)