In an era of significant technological and geopolitical changes, ASML, the number one player in the semiconductor industry, stands at a crossroads. The forthcoming retirement of Martin van den Brink and Peter Wennink, who have jointly steered ASML for over a decade, signals the end of a dynamic period. Van den Brink's leadership in technology development propelled ASML to unparalleled heights in the lithography sector, while Wennink’s diplomatic and financial acumen solidified its market dominance. ASML's impact extends beyond technology; it has become a geopolitical force, enhancing the Netherlands and Europe's strategic significance in global politics.

As ASML approaches its 40th anniversary in April 2024, it confronts a changing landscape. The company has weathered various phases – from early struggles to market leadership, marked by innovations like the PAS 5500 and immersion lithography. Under Van den Brink, ASML prioritized technological advancement, often at the expense of other factors like reliability.

The appointment of Christophe Fouquet as the incoming CEO heralds a new era. Fouquet faces the challenge of maintaining ASML's technological edge while adapting to a market nearing the limits of Moore's Law. The shift in focus from chip performance to system-level advancements requires a nuanced approach. Additionally, as technology matures, reliability and predictability become crucial for maintaining ASML's competitive edge.

The transition from a "firefighter" engineering culture to one emphasizing process and reliability won't be easy. Fouquet must balance innovation with operational efficiency, ensuring ASML remains responsive to market and geopolitical dynamics. This requires a departure from the legacy of Van den Brink, focusing instead on a holistic, structured approach to development and engineering.

Fouquet's tenure will be pivotal in shaping ASML's future. His leadership must navigate the complexities of a highly competitive industry, geopolitical pressures, and the evolving technological landscape. The challenge lies in fostering a culture that values reliability and process without stifling the innovative spirit that has been ASML's hallmark. As the company moves into its fifth decade, its ability to adapt and evolve under Fouquet's guidance will determine its continued success in a rapidly changing world.

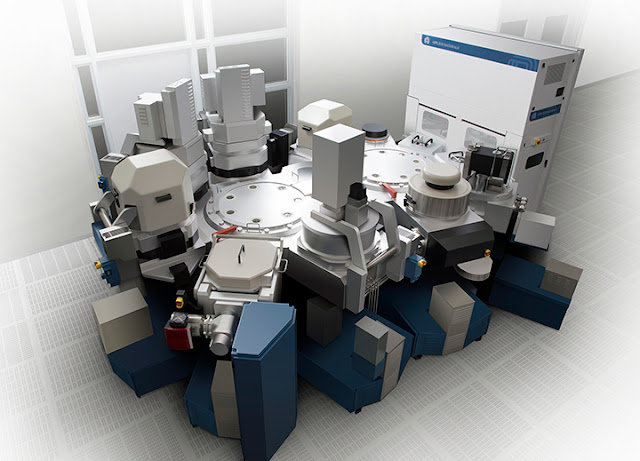

Advancing the Microchip Revolution: EUV Lithography's Challenges and Future OutlookExtreme Ultraviolet (EUV) lithography represents a significant advancement in semiconductor manufacturing, enabling the production of more compact and efficient integrated circuits, particularly for 7 nm Logic process nodes and below and leading edge DRAM. This technology, developed and marketed primarily by ASML Holding, uses a highly specialized process involving laser-pulsed tin droplet plasma to etch patterns onto substrates at the 13.5 nm wavelength scale. The progression from early prototypes to more efficient models has been remarkable, with modern EUV systems capable of handling 200 wafers per hour, a substantial improvement from initial prototypes.

Looking into the future, EUV lithography is expected to play a critical role in advancing semiconductor technology, especially as the demand for smaller and more powerful chips increases. However, several technological challenges need addressing continiously to fully harness EUV's potential:

1. Optical Component Durability: The EUV process requires highly specialized and sensitive optical components, including mirrors and photomasks. These components are prone to degradation from exposure to high-energy photons and contaminants. Improving their durability and developing efficient cleaning and maintenance processes are crucial.

2. Throughput Efficiency: While significant improvements have been made, further enhancing the throughput of EUV systems is vital. This includes reducing setup times, increasing the speed of the lithography process, and minimizing downtime due to maintenance or component replacement.

3. Pattern Fidelity and Defect Reduction: As circuit patterns become increasingly smaller, maintaining pattern fidelity and reducing defects is challenging. This involves improving the resolution of EUV systems, enhancing photoresist materials to better respond to EUV exposure, and developing more effective methods to mitigate the impact of secondary electrons generated during the lithography process.

EUV Lithography - Balancing Technological Advancements with Energy Challenges

EUV lithography, pivotal in advanced semiconductor manufacturing, faces significant energy consumption challenges. The generation of EUV light, typically via laser-pulsed tin plasma, is inherently energy-intensive. Additionally, maintaining the necessary vacuum environment and cooling systems for these high-precision machines further escalates energy use. As EUV technology becomes more prevalent, especially for producing smaller, more efficient chips, optimizing energy efficiency is critical. Future developments are expected to focus on more efficient light sources, improved system design for energy conservation, and advanced thermal management, aiming to reduce the overall energy footprint of EUV lithography processes.

EUV Lithography's Hydrogen Demand: A Growing Concern in Chip Manufacturing

EUV Lithography, also raises concerns regarding its significant hydrogen consumption. The EUV process relies heavily on hydrogen gas to maintain the cleanliness of the optical elements, particularly for preventing tin deposition on the mirrors. The need for a continuous supply of hydrogen to facilitate this cleaning process contributes to the overall operational costs and resource demands of EUV systems. As EUV technology becomes more widespread in chip manufacturing, addressing the sustainability and efficiency of hydrogen usage will be essential, both from an environmental and economic perspective.

In EUV lithography, managing hydrogen usage presents distinct challenges. The technology requires hydrogen for removing contaminants from critical mirrors, demanding systems capable of handling high volumes while maintaining vacuum integrity. This necessity places a premium on innovative system designs that minimize the footprint and energy consumption associated with hydrogen management, directly impacting the cost and efficiency of semiconductor manufacturing. Safety considerations, given hydrogen's flammability, are paramount. Advanced, fuel-free hydrogen management strategies are employed to ensure safety and environmental compliance. These strategies focus on reducing flammability risks and eliminating the need for additional fuels, thereby minimizing carbon emissions and contributing to sustainable manufacturing practices.

Continued research and development in these areas are essential for the advancement of EUV lithography, ensuring it meets the rapidly evolving demands of the semiconductor industry.

Sources:

Christophe Fouquet’s ASML must reinvent itself – Bits&Chips (bits-chips.nl)

www.imec.be

www.edwards.com

Wikipedia

2023 update to IRDS roadmap reminds key EUV issues.

— Fred Chen (@DrFrederickChen) December 28, 2023

1. EUV dose triples every four nodes => increasing electron blur?

2. EUV cannot replace multiple patterning, even with higher NA.https://t.co/hZzkfKGfyr

%20(1).png)

.jpg)

.png)