Every four years, the PRiME Joint International Meeting is held under the auspices of the Electrochemical Society (ECS), joint with its sister Societies of Japan and Korea. This fall,

PRIME 2024 will be held on Oct. 6-11, 2024 in Honolulu, Hawaii, and is expected to gather over 4000 participants and 40 exhibitors from both academia and industry.

The conference has a strong focus on emerging technology and applications in both solid-state science & technology and electrochemistry.

General information and the Meeting Program can be found here:

CALL FOR PAPERS.

The organizers of symposium G01 on “Atomic Layer Deposition & Etching Applications, 20” encourage you to submit your abstract(s) on topics, comprising but not limited to:

1. Semiconductor CMOS applications: development and integration of ALD high-k oxides and metal electrodes with conventional and high-mobility channel materials;

2. Volatile and non-volatile memory applications: extendibility, Flash, MIM, MIS, RF capacitors, etc.;

3. Interconnects and contacts: integration of ALD films with Cu and low-k materials;

4. Fundamentals of ALD processing: reaction mechanisms, in-situ measurement, modeling, theory;

5. New precursors and delivery systems;

6. Optical, photonic and quantum applications; applications aiming at Machine Learning, Artificial Intelligence

7. Coating of nanoporous materials by ALD;

8. Molecular Layer Deposition (MLD) and hybrid ALD/MLD;

9. ALD for energy conversion applications such as fuel cells, photovoltaics, etc.;

10. ALD for energy storage applications;

11. Productivity enhancement, scale-up and commercialization of ALD equipment and processes for rigid and flexible substrates, including roll-to-roll deposition;

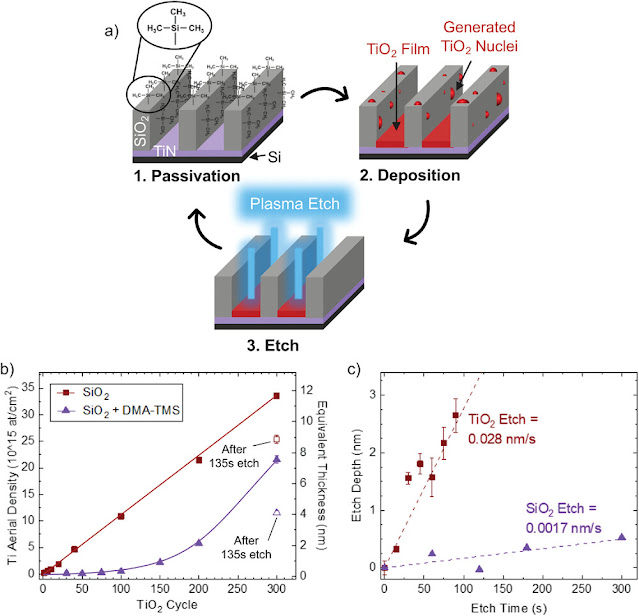

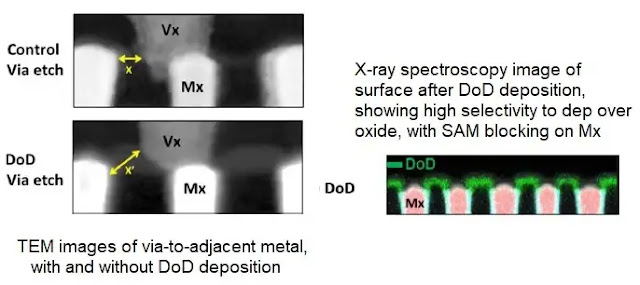

12. Area-selective ALD;

13. Atomic Layer Etching (‘reverse ALD’) and related topics aiming at self-limited etching, such as atomic layer cleaning, etc.

FYI: Last year in Gothenburg, our symposium G01 on ALD & ALE Applications 19 attracted a record number of 78 presentations, composing a full 4-day schedule of 66 oral (of which 18 invited), plus 12 poster presentations.

We will traditionally attract more attendants from Far East and expect to be as successful this fall in Hawaii.

Abstract submission

Meeting abstracts should be submitted not later than the deadline of April 12, 2024 via the ECS website:

Submission Instructions

Invited speakers

List of confirmed invited speakers (from North America, Asia and Europe):

1. Bart Macco, TU Eindhoven, Netherlands, Review of ALD for solar cells

2. Maarit Karppinen, Aalto University, Finland, ALD/MLD for energy / membrane technology

3. Chad Brick, Gelest, USA, Silanes and silazanes precursors for Area Specific Deposition

4. Makoto Sekine, Nagoya Univ., Japan, Low damage ALE of AlGaN

5. Rong Chen, HUST Univ. Wuhan, China, ALD for Cataysis and other applications

6. Mikhael Bechelany, IEM, Montpellier, France, Recent Advancements and Emerging Applications in ALD on High-Porosity Materials

7. Miika Mattinen, Univ Helsinki, Finland, ALD of dichalcogenides for electrocatalysis

8. Bonggeun Shong, Hongik University, Korea, Theory of area-selective ALD

9. Miin-Jang Chen, National Taiwan Univ., Inhibitor-free Area-Selective ALD

10. Hyungjun Kim, Yonsei University, Korea, ALD of “Group 16 Compounds” for Emerging Applications (2D TMDCs)

11. Agnieszka Kurek, Oxford Instruments, United Kingdom, Faster ALD for Emerging Quantum Applications

12. Matthew Metz, Inte, USA, Keynote on "Materials Challenges in Future Semiconductor Devices"

13. Junling Lu, University of Science and Technology of China, ALD for Catalysis

14. Sung Gap Im, KAIST, Korea, Vapor-phase Deposited Functional Polymer Films for Electronic Device Applications

15. Jason Croy, Argonne National Lab, USA, Next-gen batteries & ALD

16. Mark Saly, Applied Materials, USA, Key Challenges in Area Selective Deposition: from R&D Scale to High Volume Manufacturing

Visa and travel

In addition, Mrs. Francesca Spagnuolo at the ECS (

Francesca.Spagnuolo@electrochem.org) can provide you with an official participation letter issued by the Electrochemical Society.

We are looking forward to meeting you all at our symposium G01 on ALD & ALE Applications 20, in Honolulu | Oct. 6-12, 2024 !

%20(1).png)