Tuesday, September 17, 2024

Technological Innovations in Semiconductor Manufacturing: Insights from Tokyo Electron's 2024 Integrated Report

Thursday, February 15, 2024

AMEC's Revenue Grows with Advanced Etch Technology Fueling China's Semiconductor Surge

Monday, June 19, 2023

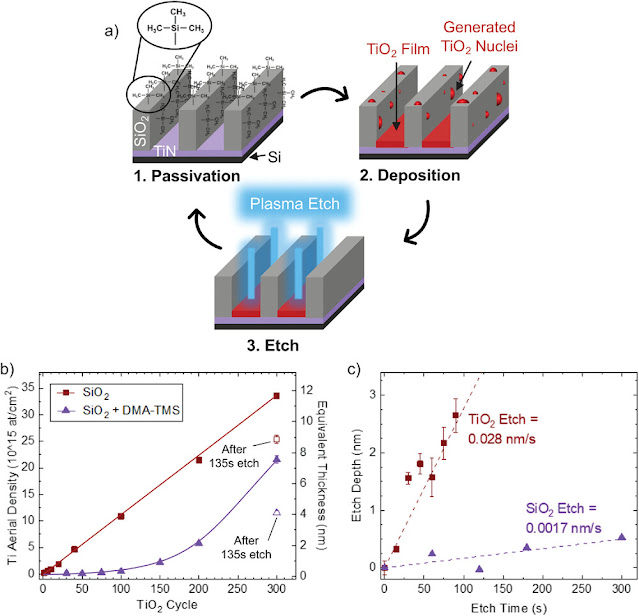

Revolutionary Study Unveils Enhanced Uniformity and Selectivity in TiO2 Films for Nanoelectronics Manufacturing

Researchers Achieve 2× Improvement in TiO2 Film Thickness and Pattern-dependent Uniformity in 45 nm Half-pitch Patterns

Monday, December 19, 2022

Foundations of atomic-level plasma processing in nanoelectronics (Open Access)

Foundations of atomic-level plasma processing in nanoelectronics

Friday, September 9, 2022

Semiconductor Equipment Consumables - Silicon Parts, in High Demand with Continued Shift Toward Asia

For more information details on the Silicon Parts market and growth trajectory, go to: https://lnkd.in/gM9GMNUs

Monday, May 3, 2021

APTC from South Korea is developing CVD, ALD and oxide etcher systems as it expands its portfolio

Friday, September 18, 2020

Process Power: The New Lithography - Advanced Energy

Here is a very insightful article by PETER GILLESPIE, VP & GM, Semiconductor Products, Advanced Energy Industries on the progress of Plasma RF Generators and Matching Networks. The article looks at applications in 3DNAND High Aspect Ratio Contacts (HARC) and Logic FinFET transitor fabrication using reactive ion etching and plasma CVD using the latest plasma technology. This is a an articel in a series of three in SEMICONDUCTOR DIGEST entitled “Process Power Steps Out from the Shadows,” looking at the leading edge technology node process challenges to highlight key drivers that are fundamentally transforming the role and importance of process power.

Process Power: The New Lithography (SEMICONDUCTOR DIGEST, LINK)

"Evolution of RF power supplies (plasma generators) and RF matching networks. Today’s RF power delivery systems are highly sophisticated with frequency tuning, complex pulsing regimes, and agile micro-second response." (Below)

Wednesday, March 4, 2020

Lam’s new Sense.i Etch platform delivers industry-leading output and innovative sensor technology

- Lam Research (NASDAQ:LRCX) introduces the Sense.i tool, which etches finer 3D details on silicon wafers for chips.

- The Sense.i platform enables the critical etch capabilities required to continue advancing uniformity and etch profile control for maximizing yield and lowering wafer costs

- 3D features can help Lam customers like Samsung and SK Hynix put more memory capacity into small areas such as smartphones.

With core technology evolved from Lam’s industry-leading Kiyo® and Flex® process modules, the Sense.i platform enables the critical etch capabilities required to continue advancing uniformity and etch profile control for maximizing yield and lowering wafer costs. As dimensions shrink and aspect ratios increase, the Sense.i platform is designed to support future technology inflections.

Powered by Lam’s Equipment Intelligence® technology, the self-aware Sense.i platform enables semiconductor manufacturers to capture and analyze data, identify patterns and trends, and specify actions for improvement. Sense.i also features autonomous calibration and maintenance capabilities that reduce downtime and labor costs, and delivers machine learning algorithms that allow the tool to self-adapt to minimize process variations and maximize wafer output.

The Sense.i platform has a revolutionary space-saving architecture that will help customers meet their future wafer output targets by producing more than a 50% improvement in etch output density. As semiconductor manufacturers develop smarter, faster, and denser chips, processes are rapidly growing in complexity and number of steps. This requires a greater number of process chambers in a fab and reduces total output for a given floor space. The Sense.i platform’s smaller footprint benefits either a new fab build or a fab undergoing a node-to-node technology conversion.

“Lam is introducing the most innovative etch product that has been developed in the last 20 years,” said Vahid Vahedi, senior vice president and general manager of the Etch product group at Lam Research (LRCX). “Sense.i extends our technology roadmap to meet our customers’ next-generation requirements while solving the critical cost scaling challenges they’re facing in their business. With more than four million wafers processed on Lam etch systems every month, Lam has an installed-base that provides extraordinary learning to innovate, design, and produce the best tools for semiconductor manufacturing.”

Wednesday, January 29, 2020

The Coventor's SEMulator3D software platform

Saturday, January 26, 2019

Oxford Instruments Partners ITRI for Micro LED Development with Plasma Etch Solutions

Friday, December 21, 2018

Chinese AMEC 5nm plasma etching tools verified by TSMC

Earlier in 2018 AMEC Introduced the Primo Nanova® System, which is the Company's first ICP etch Product for Chipmakers' most advanced memory and logic (LINK). Besides ICP AMEC has products based on CCP etch and platforms for TSV Etch (LINK).

Advanced Micro-Fabrication Equipment Inc. (AMEC)

AMEC is China's leading provider of advanced process technology to global manufacturers of semiconductors and solid-state lighting (SSL) products. Headquartered in Shanghai, the company is an entrenched supplier of dielectric and TSV Etch tools, helping chipmakers build devices at process nodes as low as 7nm. To date, nearly 800 AMEC process units have been positioned at 40 leading-edge semiconductor fabs across Asia. The company is also well established in Europe with AMEC MEMS tools running in production at major IDMs. In addition, with its MOCVD system, the company helps SSL manufacturers build today's most advanced LED products. To learn more about AMEC, please visit www.amec-inc.com.

Thursday, May 4, 2017

Advanced Energy sales for Plasma ALD sources show growth in Logic and 3DNAND

In the following eraingscall (Yahoo Finance) Yuval Wasserman, Advanced Energy Industries, Inc. - CEO, President and Director, had this to say about their recent design wins for Plasma ALD remote plasma sources and emerging plasma sources for etch accelerated by 3DNAND and Logic 10 nm ramp demand.

Looking ahead, solid state drives and mobile headsets continue to generate demand, leading to 3D NAND acceleration and additional foundry and logic investment in the ramp of 10 nanometers and the development of 7 and 5 nanometers. As the semiconductor capital equipment industry strives to keep pace, some OEMs are reaching maximum for capacity and tailoring their material planning accordingly. This leads us to expect our second quarter semiconductor revenues to remain at or above the first quarter's level.

Tuesday, April 7, 2015

A spatial ALD oxide passivation module in an all-spatial etch-passivation cluster concept!

F. Roozeboom, F. van den Bruele, Y. Creyghton, P. Poodt, and W.M.M. Kessels

ECS Journal of Solid State Science and Technology, 4 (6) pp. N5067-N5076 (2015). doi:10.1149/2.0111506jss

- The potential of ALD-assisted nanomanufacturing technologies like Atomic Layer Etching (ALEt) concepts derived from etch-purge-passivation/deposition-purge subroutines in (D)RIE and ALD is now clearly being recognized and promoted.

- The ongoing scaling of Moore's Law will soon require the implemention of these complementary technologies to meet the 10-nm challenges in surface and sidewall passivation of resist and feature patterns that is required to minimize interface, line edge and fin wall roughness.

- For cost reasons and flexibility in local pressure, i.e. (an)isotropy control, in the spatial etch and purge compartments one can envisage a gradual shift to the adoption of ALD-enabled RIE (we abbreviate it as ALDeRIE) in the spatial domain as well.

- Obviously, the spatially divided version is not commercially available yet and not straightforward, but – once realized for dedicated materials and topographies – it will certainly lead to far improved price-performance ratios in Atomic Layer Etching.

%20(1).png)