Saturday, October 26, 2024

Intel's Breakthrough in RibbonFET Transistor Scaling Demonstrates Silicon Viability for Future Nodes

TSMC 2nm Platform Technology Featuring Energy-Efficient Nanosheet Transistors and Interconnects

TSMC’s New, Industry-Leading 2nm CMOS Logic Platform: In a late-news paper, TSMC researchers will unveil the world’s most advanced logic technology. It is the company’s forthcoming 2nm CMOS (i.e., N2), platform, designed for energy-efficient computing in AI, mobile, and HPC applications. It offers a 15% speed gain (or 30% power reduction) at >1.15x chip density versus the most advanced logic technology currently in production, TSMC’s own 3nm CMOS (N3) platform, introduced in late 2022.

The new N2 platform features GAA nanosheet transistors; middle-/back-end-of-line interconnects with the densest SRAM macro ever reported (~38Mb/mm2); and a holistic, system-technology co-optimized (STCO) architecture offering great design flexibility. That architecture includes a scalable copper-based redistribution layer and a flat passivation layer (for better performance, robust CPI, and seamless 3D integration); and through-silicon vias, or TSVs (for power/signal with F2F/F2B stacking). The researchers say the N2 platform is currently in risk production and scheduled for mass production in 2H’ 25. N2P (5% speed enhanced version of N2) targets to complete qualification in 2025 and mass production in 2026.

Key Improvements:

- When shifting from 0.6V to 0.55V in the N3E architecture, there's a 15% reduction in speed but a 24% reduction in power.

- For N2, at 0.85V, there's a 14% reduction in speed and a 35% reduction in power compared to similar performance points in N3E.

- These efficiency improvements are essential for high-performance applications in power-sensitive environments.

Sources:

Monday, October 23, 2023

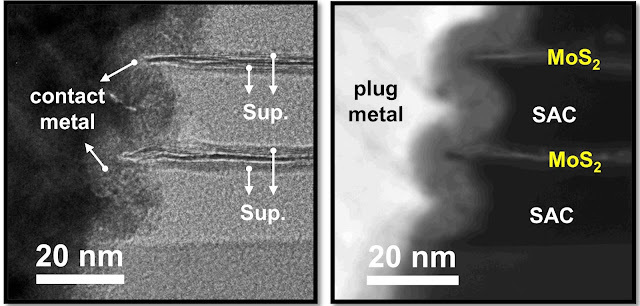

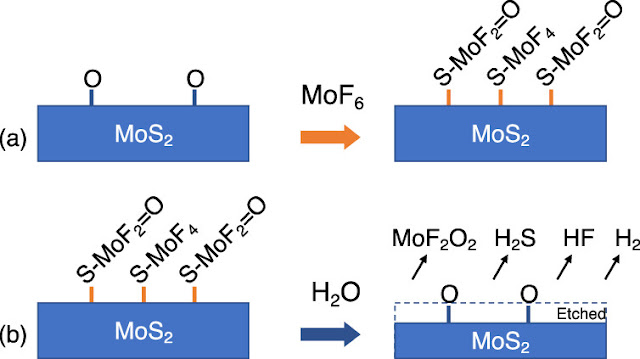

TSMC To Report Breakthrough in NMOS Nanosheets Using Ultra-Thin MoS2 Channels at IEDM 2023

Saturday, October 21, 2023

Intel Unveils Breakthrough 3D CFET Design at IEDM: Setting the Stage for Next-Gen Compact and Efficient Electronics

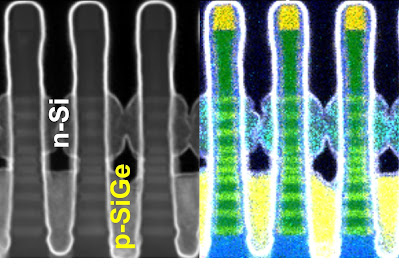

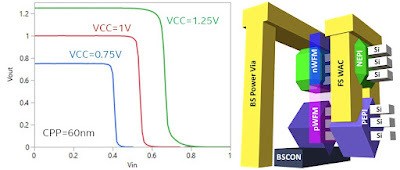

Intel researchers developed a 3D monolithic CFET device* with 3 n-FET nanoribbons atop 3 p-FET nanoribbons, separated by 30 nm gap. This industry-first device enabled the creation of functional inverters at a 60 nm gate pitch. Notably, it incorporated vertically stacked dual-Source/Drain epitaxy, dual metal work function gate stacks, and backside power delivery with direct device contacts. They also introduced a nanoribbon "depopulation" method for varying n-MOS/p-MOS device numbers. This research advances the understanding of CFET scalability for logic and SRAM applications and highlights key process enablers. The paper will be presented at the upcoming IEDM conference in San Francisco.

Comment: The stacked CMOS inverter at a 60 nm gate pitch represents an advancement in semiconductor design, allowing for denser circuits. The 60 nm distance between gates indicates a highly miniaturized design. Power vias provide vertical power connections to different layers, while direct backside device contacts enhance efficiency and heat dissipation. This development offers a glimpse into the future electronic devices being more compact, efficient, and high-performing than deploying "planar" designs in one layer like the FinFETs and GAA-FETs of today.

ALD plays a key role in manufacturing 3D monolithic CFET devices by assisting in crafting the architecture and providing atomically precise and even thin film layers at small scales. ALD ensures even coverage, which is important for 3D designs, especially on vertical areas and inside deep gaps. It's used to put down important materials in transistor gate stacks (High-k/Metal Gates or HKMG), as well as barrier and seed layers. ALD also helps in doping (SSD - solid state doping), which changes how semiconductors behave, and in creating spacers, important for separating and defining parts of transistors. In brief, ALD helps improve the CFET design and its overall performance.

* A 3D monolithic CFET device combines three-dimensional stacking and the Complementary Field-Effect Transistor (CFET) design within a single semiconductor structure. This approach vertically integrates both n-type and p-type transistors on the same substrate, promoting tighter integration and reduced interconnect delays. By leveraging the complementary operation of CFET and the benefits of 3D stacking, the device aims to enhance performance, miniaturization, and efficiency in semiconductor technology.

Friday, November 30, 2018

ASM International will host a technical luncheon seminar in IEDM 2018 San Francisco, CA, US, on Tuesday, December 4

At this technology seminar ASM will highlight the challenges and potential solutions for advanced ALD processes, equipment and productivity.

The agenda is as follows:

11:30 am Reception,food and drinks

11:55 - 12:00 pm Dr. Ivo Raaijmakers (ASM) - Welcome and introduction

12:00 - 12:30 pm Speaker: SH Hong, MSc (ASM) - "ALD for Advanced Memories"

12:30 - 1:00 pm Invited speaker: Dr. Bala Haran (IBM) - "Materials Need for the Next Era of Computing

Friday, November 9, 2018

Imec to present scaled Superduper High-k Ruthenium/Strontium titanate capacitor at IEDM

Samsung will give insights to their 3nm CMOS technology at IEDM2018

Samsung has recently stated (LINK) that they have started wafer production on its new 7LPP node (FinFET). According to the press release the process uses EUV lithography technology and demonstrates that Samsung's Foundry can follow its roadmap reaching down to 3 nm.

Sunday, October 22, 2017

Intel to present 10 nm Logic with 3rd gen FinFET and 2 level Cobalt interconnect

The graph on the left shows that the new platform maintains traditional scaling trends, while the photomicrograph on the right shows the platform’s 12-layer interconnect stack.

Reference: Paper 29.1, “A 10nm High Performance and Low-Power CMOS Technology Featuring 3rd-Generation FinFET Transistors, Self-Aligned Quad Patterning, Contact Over Active Gate and Cobalt Local Interconnects,” C. Auth et al, Intel

333 O’Farrell Street

San Francisco, CA 94102

%20(1).png)