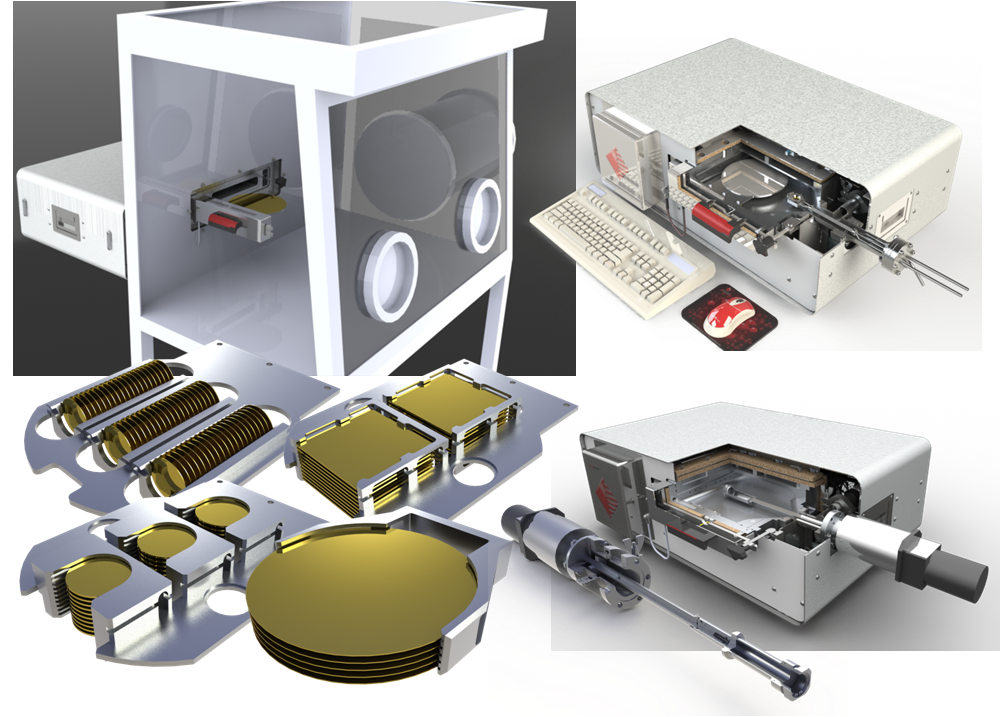

Picosun reports that they now offers new industrial ALD processes for copper and niobium oxide using the 2nd generation of the Picohot™ 300 source system.

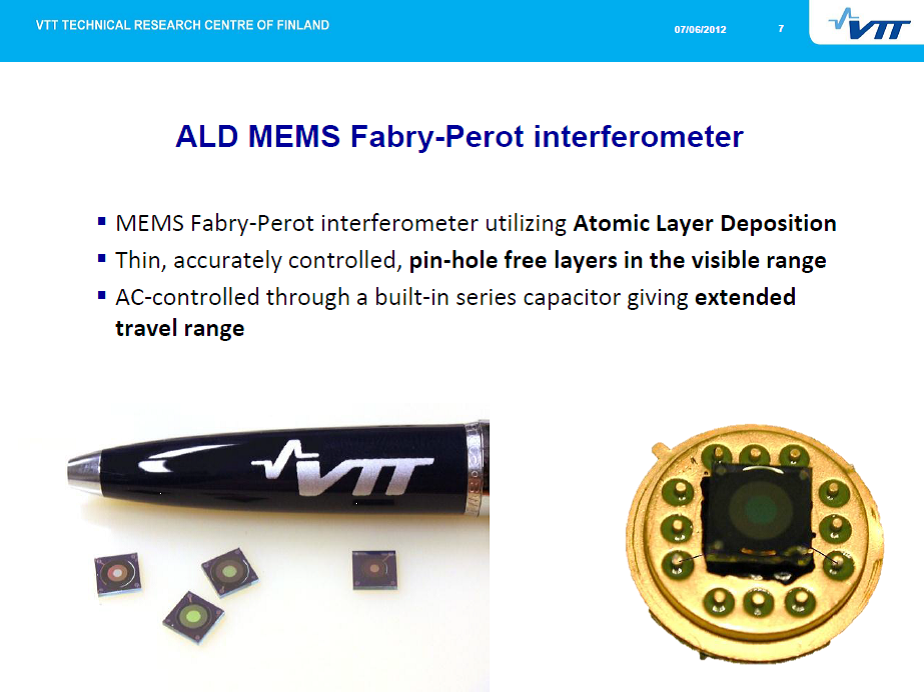

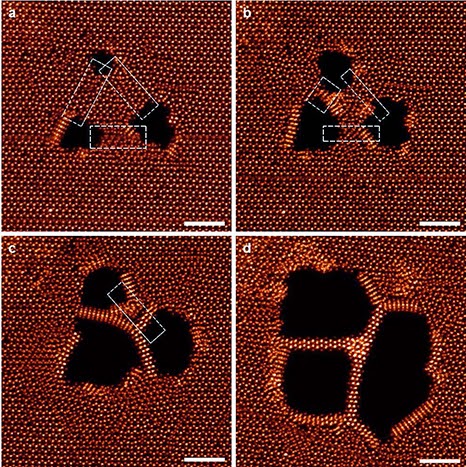

Ultra-thin copper films with the highest level of uniformity and conformality only ALD can offer as a thin film deposition method are a crucial element in today’s and future’s microelectronics and MEMS (microelectromechanical sensors) manufacturing. Copper metallization and seed layers are needed in e.g. microprocessors and 3D-integrated microelectronic components as interconnects. Niobium oxide (Nb2O5), on the other hand, is ideal for moisture and corrosion protection due to its hardness and chemical resistance.

The now developed low temperature (below 150 °C) thermal ALD processes for niobium oxide and copper have been enabled by Picosun’s newest generation of precursor source design. The 2nd generation of the Picohot™ 300 source system allows even lower vaporization temperatures and efficient, uniform distribution of the precursor vapor in the reaction chamber even at low substrate temperatures.

“Our new processes for copper and niobium oxide show again the excellent quality of Picosun’s precursor source design, allowing true ALD processing also on thermally sensitive materials such as plastics and piezoelectrical elements. On several of Picosun’s main market areas such as MEMS, microelectronics, and corrosion protection, these processes further solidify our status as the leading solution provider of the thin film coating needs of today’s industries,” states Juhana Kostamo, Managing Director of Picosun.

Ultra-thin copper films with the highest level of uniformity and conformality only ALD can offer as a thin film deposition method are a crucial element in today’s and future’s microelectronics and MEMS (microelectromechanical sensors) manufacturing. Copper metallization and seed layers are needed in e.g. microprocessors and 3D-integrated microelectronic components as interconnects. Niobium oxide (Nb2O5), on the other hand, is ideal for moisture and corrosion protection due to its hardness and chemical resistance.

The now developed low temperature (below 150 °C) thermal ALD processes for niobium oxide and copper have been enabled by Picosun’s newest generation of precursor source design. The 2nd generation of the Picohot™ 300 source system allows even lower vaporization temperatures and efficient, uniform distribution of the precursor vapor in the reaction chamber even at low substrate temperatures.

“Our new processes for copper and niobium oxide show again the excellent quality of Picosun’s precursor source design, allowing true ALD processing also on thermally sensitive materials such as plastics and piezoelectrical elements. On several of Picosun’s main market areas such as MEMS, microelectronics, and corrosion protection, these processes further solidify our status as the leading solution provider of the thin film coating needs of today’s industries,” states Juhana Kostamo, Managing Director of Picosun.

Picosun’s highest level ALD thin film technology enables the industrial leap into the future by novel, cutting-edge coating solutions, with four decades of continuous, groundbreaking expertise in the field. Today, PICOSUN™ ALD systems are in daily production use in numerous prominent industries around the globe. Picosun is based in Finland, with subsidiaries in USA, China, and Singapore, and a world-wide sales and support network.

%20(1).png)