A manufacturing technique that could help the semiconductor industry make more powerful computer chips began in the humblest of places — at a lunch table at the U.S. Department of Energy’s (DOE) Argonne National Laboratory.

The materials synthesis method known as sequential infiltration synthesis, or SIS, has the potential to improve not only chip manufacturing but also things like hard drive storage, solar cell efficiency, anti-reflective surfaces on optics and water-repellant car windshields. Invented in 2010 during a lunchtime conversation between Argonne scientists Seth Darling and Jeffrey Elam and two of their postdoctoral researchers, use of the method has grown in recent years.

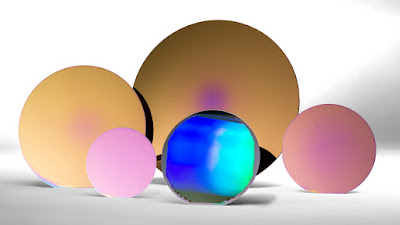

Top: Jeff Elam and Anil Mane, co-inventor on the SIS for lithography method and Principal Materials Science Engineer in Argonne’s Applied Materials Division. Bottom: Silicon wafers, ranging in size from 4” to 12” diameter, that have been treated using Argonne’s sequential infiltration synthesis method (Credit : Argonne National Laboratory).

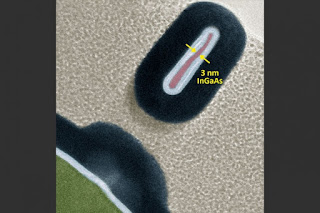

The method was based on the group’s discussion of atomic layer deposition, or ALD, a thin film deposition technique that uses alternating chemical vapors to grow materials one atomic layer at a time. Darling, director of the Institute for Molecular Engineering at Argonne and the Advanced Materials for Energy-Water Systems Energy Frontier Research Center, recently used that technique to add a water-loving metal oxide coating to filters used in the oil and gas industry which prevents the filters from clogging.

“It worked beautifully on the first try.” — Seth Darling, director of Argonne’s Institute for Molecular Engineering and the Advanced Materials for Energy-Water Systems Energy Frontier Research Center

But as the group talked, they started speculating about taking ALD to a new level, said Darling.

“We said ‘Wouldn’t it be neat if we could grow one material inside another material like a polymer (a string of many combined molecules) instead of on top of it?’” Darling said. “We first thought ‘This isn’t going to work,’ but, surprisingly, it worked beautifully on the first try. Then we began imagining all of the different applications it could be used for.”

The research was funded by the DOE Office of Science, Basic Energy Sciences Program as well as the Argonne-Northwestern Solar Energy Research Center, a DOE Office of Science-funded Energy Frontier Research Center.

Anil Mane unloding wafers processed in a BENEQ TFS 500 ALD reactor at Argonne’s Applied Materials Division. (Credit : Argonne National Laboratory).

SIS is similar to ALD on a polymer surface, but in SIS the vapor is diffused into the polymer rather than on top of it, where it chemically binds with the polymer and eventually grows to create inorganic structures throughout the entire polymer bulk.

Using this technique, scientists can create robust coatings that can help the semiconductor manufacturing industry etch more intricate features on computer chips, allowing them to become even smaller or to add extra storage and other capabilities. They can also tailor the shape of various metals, oxides and other inorganic materials by applying them to a polymer with SIS and then removing the remains of the polymer.

“You can take a pattern in a polymer, expose it to vapors and transform it from an organic material to an inorganic material,” said Elam, director of Argonne’s ALD research program, referring to the way the method can use polymers and a vapor to basically mold a new material with specific properties. “It’s a way to use a polymer pattern, and convert that pattern into virtually any inorganic material.”

The technology’s potential spans beyond semiconductors. It could be used to advance products in different industries, and Argonne would be delighted to work with commercialization partners who can take the invention and incorporate it in existing products - or invent new applications to benefit U.S. economy, said Hemant Bhimnathwala, a business development executive at Argonne.

“You can use SIS to create a film, you can put it on a metal, you can create this on glass or put it on a glass windshield to make it water repelling to the point where you don’t need wipers,” Bhimnathwala said.

The way the scientists invented the technique — through that lunch meeting — was also a bit unusual. New discoveries often come about by accident, but not usually by spitballing ideas over lunch, Elam said.

“Occasionally, if you’re watching intently, you can see something else there and discover something new and unexpected,” Elam said. “That doesn’t happen very often, but when it does, it’s great.”

The technique also addresses a specific concern in the semiconductor manufacturing industry, pattern collapse, which means the collapse of tiny features used to create electrical components on a computer chip, rendering it useless.

When a pattern is etched on a silicon chip in the chip-making process, an etch-resistant surface is used as a protective coating to mask those regions you do not want to remove. But the etch-resistant coatings commonly used today wear away very quickly, which has prevented chip manufacturers from making components with deeply etched features, Darling said.

With SIS, inorganic vapor coatings can be engineered to provide greater protection of vertical features, allowing deeper etches and the integration of more components on each chip.

“Features on chips have gotten extremely small laterally, but sometimes you also want to make them tall,” Darling said. “You can’t make a tall feature if your resist etches away quickly, but with SIS it’s easy.”

Similarly, the technique can be used to manipulate magnetic recording on hard drives or other storage devices, allowing them to increase storage while also getting smaller, Darling said.

Another possibility for the technology is to control how much light bounces off a glass or plastic surface. Using SIS, scientists can engineer surfaces to be almost entirely non-reflective. Using this strategy, scientists can improve performance of solar cells, LEDs and even eyeglasses.

“There are also a lot of applications in electronics,” Elam said. “You can use it to squeeze more memory in a smaller space, or to build faster microprocessors. SIS lithography is a promising strategy to maintain the technological progression and scaling of Moore’s Law.”

The team’s research on the technology has been published in

The Journal of Materials Chemistry,

The Journal of Physical Chemistry,

Advanced Materials and

The Journal of Vacuum Science & Technology B.

Argonne is looking for commercial partners interested in licensing and developing the technology for more specific uses. Companies interested in leveraging Argonne’s expertise in SIS should contact

partners@anl.gov to learn more and discuss possible collaborations.

Top: Seth Darling, Scientist and Director of the Institute for Molecular Engineering at Argonne National Laboratory. Bottom: Jeff Elam, Senior Chemist in Argonne’ Applied Materials Division (bottom). Picture Credit : Argonne National Laboratory.

%20(1).png)