Hydrogen peroxide (H2O2) gas is an oxidant that improves passivation and nucleation density at semiconductor interfaces, potentially leading to reduced interfacial defect density. A new technology capable of generating and delivering stable anhydrous H2O2 gas has been developed by RASIRC. The method utilizes a substantially anhydrous H2O2 solution, a carrier gas and membrane pervaporator in order to deliver anhydrous H2O2. A broad range of high-k materials and interfaces that can be improved as well as enhanced transistor performance were shown at ALD2016 Ireland.

H2O2 allows for unique process windows in ALD due to its oxidative potential, which lies between more commonly used water and ozone, and greater acidity relative to water [1]

RASIRC BRUTE H2O2 Apparatus (H2O2 + solvent) surrounds the Nafion membrane tubes. H2O2 passes through the membrane walls and is picked up by the carrier gas.

Growth of many different films has been showcased with

BRUTE Peroxide and the related RASIRC product BRUTE Hydrazine. In

presentations and posters at ALD2016 Ireland the RASIRC line of BRUTE

Hydrazine and BRUTE Peroxide showed impressively many useful

results by many different precursors. In total, four separate posters

and presentations covered growth passivation of SiOx on SiGe, SiNx on SiGe, SiON on SiGe as well as growing HfO2, ZrO2, TiO2, Al2O3 and TaOx with the BRUTE line of new reactive chemistries.

Transistor channel passivation, Dan Alvarez presented results of growing SiNx and SiOxNx on SiGe using BRUTE Hydrazine and BRUTE Peroxide [2]. These films were then further processed with HfO2

dielectric layer to grow MOSCAPs. These MOSCAPS had better performance

than those processed with HF last and water vapor, where improved defect

density and lower leakage characteristics were reported. In addition,

the presentation by Dan Alvarez discussed how anhydrous hydrazine can be

used to create a thin layer of silicon nitride that can act as a

diffusion barrier or channel passivation layer prior to dielectric

deposition in FinFets or MOSFETs. The study focused on <400 °C

silicon nitride ALD process and showed how further oxidation using

anhydrous peroxide provides good nucleation for High-k deposition.

A low

Temperature Passivation on SiGe(110) via plasma free process by

subsequent doses of anhydrous hydrazine and hexachlorodisilane can

further increase the amount of SiNx on the surface. A final treatment

with HOOH can prepare the surface for high-k deposition.

BRUTE Peroxide was reported to reduce HfO2 gate oxide EOT by reduction in the interface layer

Steve Consiglio from Tokyo Electron, presented data comparing growth of HfO2 and interface layer thickness control [3]. Utilizing

300 mm Si wafers with pre-formed chemical oxide, he evaluated an all

in-situ method of chemical oxide removal (COR; Si-H termination)

followed by H2O2(g) dosing prior to ALD growth of HfO2 using TEMAHf and H2O. The study reported faster growth rate with H2O2 than for O3.

Most interestingly, the interface results were very exciting with

interface layer regrowth in the 2-4 Ångstrom range, which corresponds to

½ to 1 monolayer of SiOx interface for improved EOT and this was

definitely much thinner than the results reported using O3.

Aluminum oxide, Al2O3 ALD has been presented previously [4]. This time RASIRC had a poster on improved nucleation by using H2O2 as an oxidant in ALD of Al2O3

[5]. The poster explained the need for a novel oxidant that improves

passivation and nucleation density at semiconductor interfaces. The

study was performed on SiGe(110) surfaces and provides a direct comparison of equal amounts of water, 30% H2O2/H2O, and anhydrous H2O2. A five-fold increase was found in nucleation density for H2O2 versus water, and a three-fold increase for H2O2 versus 30% H2O2/H2O. An additional comparison was made of H2O2 to H2O by deposition of Al2O3 on an Si-H surface. This comparison found denser nucleation and faster initiation for H2O2 treated surfaces.

In a direct

comparison of TMA based ALD with water vs peroxide the coverages of O

and Al are higher with peroxide and growth starts earlier.

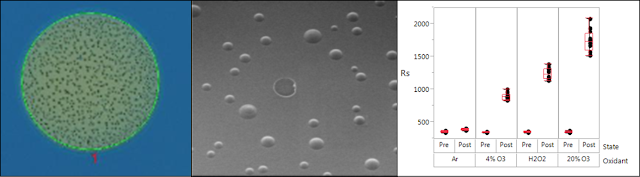

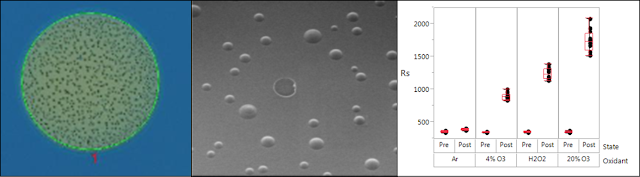

Zirconium oxide, ZrO2 was presented in study by Intermolecular and RASIRC at ALD2016 Poster session [6]. By utilizing the Intermolecular Combinatorial ALD platform equipped with a RASIRC BRUTE H2O2 apparatus the study compared the performance of H2O2 against O3 in a zirconium oxide ALD using ZyALD Air Liquide industry standard Zr-precursor. By MIMCAP integration the differences in ZrOx unit film properties and electrical performance was shown. Similar unit film behavior (GPC, linearity, growth saturation, film crystallinity etc.) was observed between O3 and H2O2.

Oxidant dosing (left) show that 4% O3 yields saturated response, whereas H2O2 and 20% O3 display softer saturation. ZyALD dose (middle) for each oxidant system shows definite completion for 20% O3. All three investigated conditions show linear growth without growth inhibition (right).

The MIMCAP study (above) concluded that ZrO2 produced with H2O2 matched the best performance of 4% O3. Therefore it is possible to avoid issues observed with high (20%) O3 concentration as showcased in the figure below. More importantly, H2O2 has the capability to produce thin node dielectric, which is needed for highly scaled DRAM nodes.

Optical (left) and SEM (middle) images of MIMCAPs, post-annealing, with defects observed with 20% O3 and thin 5 nm ZrOx. As comparison blanket TiN film enhanced resistivity was observed (right) using 4 resp. 20% O3 concentrations, whereas H2O2 lays in-between. Results suggest that elevated TiN bottom electrode oxidation takes place with 20% O3 that leads to degassing during annealing. However, the defect can be avoided with minimal reduction in growth rate, by using H2O2 as the oxidant.

Hafnium oxide, HfO2

by TDMAHf along TEMAHf was the first Hf-precursors in use at the

introduction of High-k in the DRAM industry more than 10 years ago at

the 90nm node. HfO2 ALD has also been investigated by Intermolecular using the H2O2/TDMAHf ALD process and in this study the MIMCAPs showed to match the best O3 performance like in the case of ZrO2 given in more detail above. In addition, Tokyo Electron presented work for HfO2 as summarized above.

Titanium oxide, TiO2 low temperature (100 °C) TiOx ALD using H2O2 and TiMCTA (methylcyclopentadienyl tris(dimethylamino)titanium) as the metal precursor has successfully been grown as also reported by Intermolecular at ALD2016 Poster session [6].

To summarize, RASIRC and their collaborations throughout

the semiconductor insdustry and with leading research facilities have

shown that many different films can be grown with BRUTE Peroxide and

BRUTE Hydrazine and most importantly that BRUTE Peroxide can reduce EOT

by reduction in the interface layer, yielding higher performing memory

and logic devices.

References

[1] D. R. Lide, CRC Handbook of Chemistry and Physics (CRC Press, Boca Raton, 1996).

[2] Hydrogen peroxide gas for improved nucleation and

initiation in ALD, Daniel Alvarez, Adam Hinckley, Pablo Macheno,

Christopher Ramos, Jeffrey Spiegelman,

Anthony Muscat, Presentation at ALD 2016 Ireland.

[3] Anhydrous H2O2 for ALD HfO2

growth and interfacial layer thickness control, Steven Consiglio,

Robert Clark, Takahiro Hakamata, Kandabara Tapily, Cory Wajda, Gert

Leusink, Presentation at ALD2016 Ireland.

[4] Comparison of Water Vapor to Ozone for Growth ALD

Films, J. Spiegelman, J. Sundqvist, EU PVSEC Proceedings 2011, page 1694

– 1698.

[5] Hydrogen peroxide gas for improved nucleation and

initiation in ALD, Daniel Alvarez, Adam Hinckley, Pablo Macheno,

Christopher Ramos, Jeffrey Spiegelman, Anthony Muscat, Poster ALD2016

Ireland.

[6] Comparison of hydrogen peroxide and ozone for use in zirconium oxide atomic layer deposition, Gregory Nowling, Stephen Weeks, Daniel Alvarez, Mark Leo, Jeff Spiegelman, Karl Littau, Poster ALD2016 Ireland.

%20(1).png)