Similarities with TSMC 7nm have been found

After TechInsights revealed their initial findings on the SMIC MinerVa Bitcoin mining processor, their team did further analysis and comparison against TSMC 7nm. This new analysis confirms that despite current sanctions restricting access to the most advanced equipment technologies, Chinese Semiconductor Manufacturing International Corporation (SMIC) has used 7nm technology to manufacture the MinerVa Bitcoin Miner application-specific integrated circuit (ASIC).

The TechInsights analysis also uncovered many similarities between the SMIC 7nm and the TSMC 7nm, which are available in our comparison brief.

According to the SeekingAlpha assessment earlier this year (Applied Materials: SMIC Move To 7nm Node Capability Another Headwind (NASDAQ:AMAT) | Seeking Alpha) SMIC is using a large amount of multiple pattering mask layers like in the first TSMC and Samsung 7 nm nodes (N7).

"At 7nm, normally 15 DUV systems and 5 EUV systems are demanded, depending on chip type and company. However, since SMIC is not permitted to use EUV, then they will be substituted by DUV, and 20 DUV systems will be used.

In both cases, multiple patterning is done to delineate that pattern, whether it is 28nm or 7nm. This multiple patterning process is more or less a trick to reach even the 28nm dimensions. The multiple patterning is typically a combination of deposition, etch, and lithography steps.

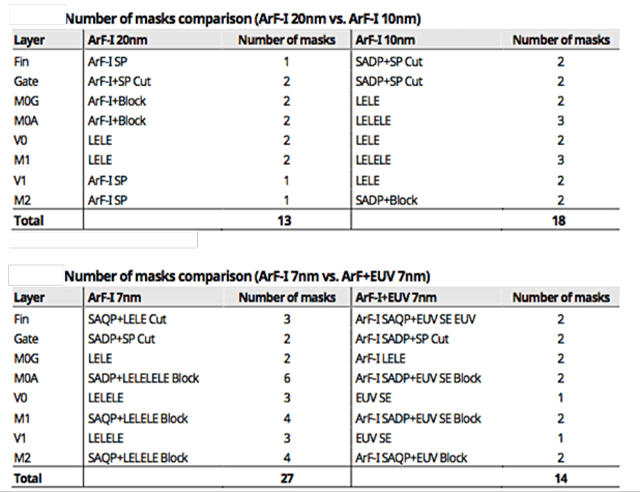

If we look at Chart 3 below, using immersion DUV (ArF-1) at the 20nm node there are 13 mask layers, each of which uses multiple dep-etch steps. If we move across the top of the chart, at 10nm there are 18 mask layers, an increase of 50% in the use of deposition-etch steps.

Multiple patterning at the 7nm node, as shown in the bottom left of the chart, requires 27 mask layers. However, by switching to EUV (bottom right) at 7nm, only 14 mask layers are required, similar to the 20nm node with DUV.

The terminology is as follows in switching from DUV to EUV:Double litho, double etch (LELE) process will be eliminated

While ArF-I would continue to be used for the self-aligned double patterning (SADP) and

Self-aligned quadruple patterning (SAQP) processes."

Table from SeekingAlpha as cited above

From an ALD point of view, the FEOL and metallization up to M2 use 19 in the case of Immersion Lithography (N7) vs 10 in the case of EUV (N7+) ALD spacer-defined multiple patterning masks (SADP or SAQP). However, the bigger difference is in etch for LELE etc., where EUV N7+ uses only 2 such masks.

%20(1).png)