On the 10th of February, 2021, Prof. Erwin Kessels from Eindhoven University of Technology, Netherlands, delivered a 4-hour long webinar, full of highly valuable content, on Plasma-Assisted (Enhanced) Atomic Layer Deposition (PAALD/PEALD). For those who missed this wonderful opportunity to have an insight into one of the most advanced deposition processes in the semiconductor chip production line today, Abhishekkumar Thakur, Associated Technology Analyst with BALD Engineering AB has come up with some interesting highlights and key takeaways from Prof. Kessels' webinar from when we took part:

February 10, Erwin Kessels will present an AVS Webinar: Plasma-Assisted Atomic Layer Deposition: From Basics to Applications. Learn more at https://avs.swoogo.com/webinar_pald

Interesting Highlights and Key Takeaways

1. The current deposition wafer fab equipment market size for ALD has grown as big as or even bigger than that for PVD (Physical Vapor Deposition), but still less than that for CVD (Chemical Vapor Deposition)

2. Semiconductor processing plasmas exist under non-equilibrium conditions, i.e., the electrons present in the plasma are heated by the applied electric field up to a temperature of 50,000 K (~5eV) as opposed to the relatively low gas temperature (300-500 K) due to the low pressures. This is the reason that PEALD becomes useful in the deposition of the high-quality thin-films on thermally fragile substrates/structures, e.g., plastic, foil, photoresist, etc.

3. Electron Energy Distribution Function (EEDF) together with the electron impact cross-section with the events occurring in the plasma (e.g. dissociation, excitation, ionization, etc.) determines the density of a particular species in the plasma (e.g. ions, radicals, etc.)

Ref:

https://doi.org/10.1116/6.00001454. The thickness of the plasma sheath is typical ~0.1 to 10mm depending on the electron density, the electron temperature, and the potential difference between the plasma and the surface in contact with the plasma (the larger the potential difference is, the thicker the sheath is). The plasma sheath bends along the surface of the macroscopic objects and ions strike every surface of the object orthogonally. However, the plasma sheath can’t follow the surface of the microscopic features (e.g. microscopic trenches in a wafer), thus the ions bombard only the top and the bottom flat surfaces of the features.

5. Plasma source can also be a big source of Oxygen contamination when gets eroded by ion bombardment. It’s especially a big problem in the PEALD of nitrides in ICP systems. In this regard, the use of Alumina as a dielectric window in an ICP system can lead to less sputter yield than that from the use of Quartz as a dielectric window, thereby providing better quality nitride films. This is the reason why many companies have adopted Hollow Cathode Plasma source developed by Meaglow Ltd. in their systems.

6. Vacuum systems themselves can also be a source of Oxygen contamination, especially the ALD reactors because they typically don’t have very low base pressure; usually ~10-6 Torr after utilizing a turbo molecular pump. If the ALD cycle times are relatively long such that the reactive surfaces are exposed to the (“poor”) vacuum for a relatively long time, the Oxygen concentration in the deposited film increases. In other words, the faster the ALD process is, the less contaminated the deposited film is.

7. Strong pumping does not only lead to a better vacuum and in turn less Oxygen contamination in the deposited film, but it also helps reduce the gas residence time inside the reactor minimizing the surface reaction by-products being cracked in the plasma and redepositing on the surface. Thus, a higher pumping speed results in a higher quality film growth.

8. Regarding the conformal growth of an ALD film: When S0*AR2 < 0.1, the film growth is reaction-limited, and extending the precursor/co-reactant dose (beyond the saturation dose) will not make any difference in the film conformality. It’s similar to the growth on a planar substrate. However, when S0*AR2 > 100, the film growth is diffusion-limited, and hence, the precursor/co-reactant dose, that needs to be applied to get a fully conformal growth in the trench, scales with the AR2. In the case of PEALD, the film growth can be recombination limited too, and it becomes even difficult to get a conformal film growth because of the co-reactant dose that needs to be applied to get a fully conformal growth in the trench scales exponentially with the AR. The conformality becomes further difficult to achieve when the surface recombination probability r of the radicals strengthens. Moreover, the conformality of the PEALD film depends heavily on the film material to be deposited because the surface recombination probability of the radicals heavily depends on the material, e.g., SiO2 films can go much deeper into the trench than Al2O3 or HfO2 films since the surface recombination probability of O radicals on SiO2 is much lower than that on Al2O3 or HfO2. The surface recombination probability also depends on the substrate temperature and the process pressure.

[S0 = Sticking probability with zero surface coverage, AR = Aspect Ratio of the trench]

9. PEALD film properties are strongly dependent on ion-energy dose = plasma exposure time*ion flux*mean ion energy. By applying substrate biasing, i.e., by employing mild ion bombardment, mass density, refractive index, crystalline properties, resistivity, void fraction, residual stress, surface roughness, thickness uniformity, chemical composition, topographic selectivity, etc. of the deposited film can be tuned.

10. Plasma can cause radiation damage in the PEALD films because plasma also comprises radiation in the vacuum ultraviolet (VUV) region (i.e. wavelengths below 200nm) generating VUV photons that can have energy up to even 10-40 eV. However, this certainly can’t disqualify plasma processing in the semiconductor industry because there are methods to avoid the adverse impact of VUV photons, e.g., working at higher process pressure as the VUV photons are easily absorbed by the gas.

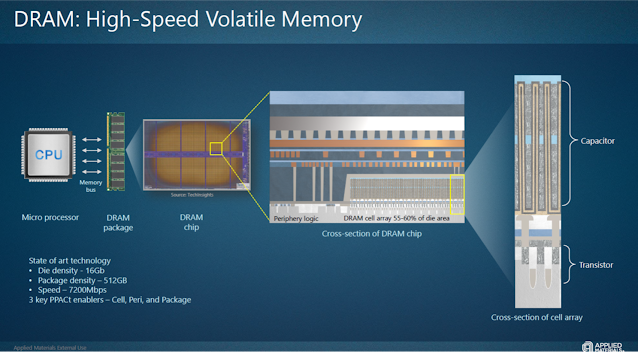

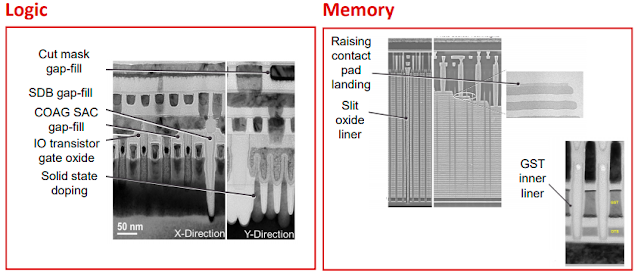

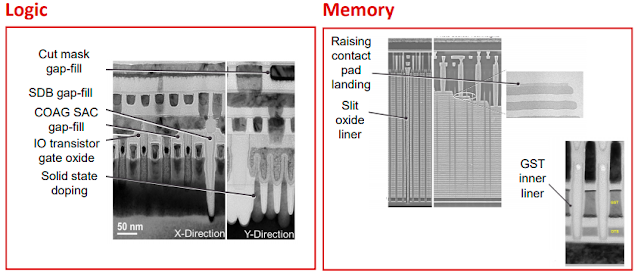

11. Some of the applications of PEALD in the Logic HVM include cut mask gap-fill, single diffusion break (SDB) gap-fill, contact over active gate (COAG) self-aligned contact (SAC) gap-fill, gate oxide for the IO transistors, solid-state doping, patterning hard-mask, etc. and in the Memory HVM include raising contact pad landing by depositing SiN, slide oxide line, GST X-point (phase-change) memory inner liner, etc. Topographically selective PEALD has been in use in 3D NAND production. The biggest PEALD market at present is that of self-aligned multiple patterning with SiO2 since 22 nm node. It’s important here to note that more than 50% of the PEALD layers are sacrificial and don’t show up in the device! PEALD of SiO2 has also been in the display market, e.g., in a barrier stack against moisture permeation in the curved plastic OLED displays in the Cadillac Escalade 2021. In addition to that, PEALD SiO2 has also found its application in the nanoscale encapsulation of perovskite nanocrystal luminescent films to enhance its stability against water, light, and heat.

%20(1).png)