The website for the 2020 Area Selective Deposition Workshop is now live! Come join us next April 2-3 at Stanford to learn about the cutting edge science being performed around the world! #Area_Selective #ASD20 #ALDep #CVDep https://t.co/MJxTgGECkf— Bent Group (@BentGroup) September 11, 2019

Thursday, September 12, 2019

The website for the 2020 Area Selective Deposition Workshop is now live!

Saturday, September 13, 2014

Scientists Come up with ALD Technique to Repair Atom-sized Graphene Defects

Graphene is pure carbon in the form of a very thin, nearly transparent sheet, one atom thick, with excellent mechanical, electrical properties. In order to apply graphene to photovoltaic cells, displays, or sensors, it must be made in large scale.

But graphene tended to crack and produce boundary lines, making it difficult to maintain excellent material properties. To address this problem, there have been attempts to deposit metal on graphene surface, which was not effective as the metal deposition was not selective enough to defective parts.

By using platinum, the research team successfully demonstrated the selective deposition of metal at chemical vapor deposited graphene’s line defects, notably grain boundaries, by atomic layer deposition. As a result, the team proved three times improved electrode and hydrogen gas sensors at room temperature. The research outcome was reported on the September 2 issue of Nature Communications (see abstract below).

Kwanpyo Kim, Han-Bo-Ram Lee, Richard W. Johnson, Jukka T. Tanskanen, Nan Liu, Myung-Gil Kim, Changhyun Pang, Chiyui Ahn, Stacey F. Bent, & Zhenan Bao

Wednesday, February 3, 2021

Call for Abstracts - The 5th AVS Area Selective Deposition Workshop (ASD 2021)

Sunday, October 25, 2015

Self-Correcting Process for High Quality Patterning by Atomic Layer Deposition

Self-Correcting Process for High Quality Patterning by Atomic Layer Deposition

Monday, February 4, 2019

Extended deadline for ASD 2019 Workshop

The workshop will feature the following invited speakers:

Rudy J. Wojtecki (IBM, USA), Katie Nardi (LAM Research, USA), Kanda Tapily (TEL, USA), Chi-I Lang (AMAT, USA), John Tolle (ASM, USA), Han-Bo-Ram Lee (Incheon National University), Gregory Parsons (NC State University, USA), Matthias Minjauw (University of Gent, Belgium), Necmi Biyikli (University of Connecticut, USA), Mohamed Saib (IMEC, Belgium), Efrain A. Sanchez (IMEC, Belgium), John G. Ekerdt (University of Texas, USA).

The workshop will cover a wide range of topics, including the following:

Area selective epitaxy and area selective chemical vapor deposition: processes and mechanisms, defects control

Intrinsic selectivity of ALD processes: nucleation and interface studies, chemical selectivity in surface reactions, competitive adsorption, precursors design, modeling of surface reactions

Methods for area selective activation / deactivation: use of inhibitors (self-assembled monolayers, polymers), plasma-/beam-induced activation

Processes and mechanisms for area selective atomic layer deposition: deposition of metals or dielectrics, thermal/plasma enhanced ALD, 3D or patterned substrates, substrates preparation, sequential deposition/etching,

Metrology and defects control: surface characterization techniques, selective etching of defects

Applications of area selective deposition: semiconductor industry (integration needs of device makers, solutions proposed by the equipment makers), catalysis, energy generation and storage, etc.

On behalf of the organizing committee, it will be our pleasure to welcome you in Leuven.

Andrea Illiberi Program Chair of the 4th ASD workshop

Sunday, July 19, 2015

Self-Correcting Process For High Quality Patterning By Atomic Layer Deposition

Self-Correcting Process For High Quality Patterning By Atomic Layer Deposition.

Wednesday, August 5, 2020

Applied Materials launch Selective Tungsten CVD for their Endura(TM) platform

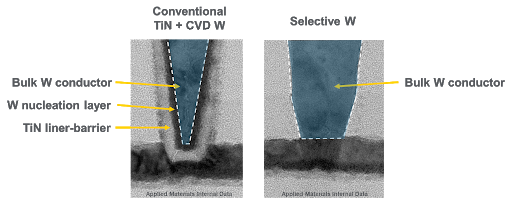

With continued scaling, however, contact dimensions have decreased to the point at which contact resistance is becoming a bottleneck in realizing optimum device performance. As the cross-sectional area of the contact shrinks, a growing proportion of the volume is occupied by metal liner/barrier and nucleation layers, leaving less volume for the conducting metal fill. In addition, multiple resistive interfaces in the plug contribute to higher contact resistance.

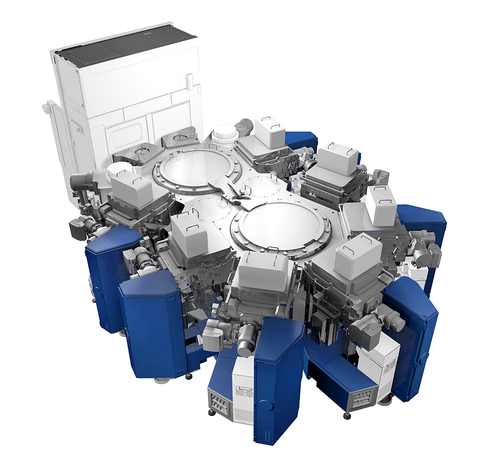

An Applied Materials Endura(TM) Platform equipped with seven Selective Tungsten CVD Volta(R) and 2 pre-clean 300 mm chambers. (Credit: Applied Materials)

The Applied Endura Volta Selective W CVD system offers an integrated materials solution that relieves these adverse effects with a breakthrough in 2D scaling. The system combines surface treatment chambers with selective tungsten deposition chambers. The selective deposition is enabled by both the unique process capabilities of the deposition chambers and the various surface treatments that use specialized chemistries to prepare the underlying metal and dielectrics of the contact to enable bottom-up, metal-on-metal deposition. The selective process eliminates both liner/barrier and nucleation layers to alleviate the bottleneck in device performance, and produces void- and seam-free gapfill.

Cross section of a leading edge Logic processor showing the Source/Drain contacts to the transistors and the metal interconnetcs (Credit: TechInsight, Applied Materials)

As all process steps are performed in an ultra-clean, continuous high-vacuum environment, the integrated materials solution ensures a pristine interface and defect-free contact fill. With the volume of conducting metal maximized, contact resistivity is substantially improved compared to conventional liner/barrier contact fabrication. This lower resistance facilitates higher device density and extends 2D scaling.

The selctive W CVD defect-free contact fill maximizes the volume of conducting metal (right), contact resistivity is substantially improved compared to conventional liner/barrier contact fabrication (left). (Credit: Applied Materials)

Monday, September 14, 2015

Area-Selective ALD : Conformal Coating, Subnanometer Thickness Control, and Smart Positioning

Area-Selective Atomic Layer Deposition: Conformal Coating, Subnanometer Thickness Control, and Smart Positioning

† Department of Physics and Materials Science, City University of Hong Kong, 83 Tat Chee Avenue, Kowloon, Hong Kong

‡ State Key Laboratory of Millimeter Waves, City University of Hong Kong, 83 Tat Chee Avenue, Kowloon, Hong Kong

§ Shenzhen Research Institute, City University of Hong Kong, Shenzhen, 518057, P. R. China

ACS Nano, Article ASAP

DOI: 10.1021/acsnano.5b05249

Saturday, March 21, 2015

Highly Selective Directional ALE of Silicon by LAM Research (OPEN ACCESS ARTICLE)

Highly Selective Directional Atomic Layer Etching of Silicon (OPEN ACCESS)

Sunday, October 30, 2016

Hot paper on selective Atomic Layer Etching using fluorination and ligand-exchange reactions

Selectivity in Thermal Atomic Layer Etching Using Sequential, Self-Limiting Fluorination and Ligand-Exchange Reactions

Monday, July 11, 2016

Applied Materials Releases Selective Etch Tool - The Producer® Selectra™ Etch system

Fulls story : http://semimd.com/blog/2016/06/29/applied-materials-releases-selective-etch-tool/

Full information as released by Applied Materials can be found here : http://www.appliedmaterials.com/products/producer-selectra-etch

Sunday, July 7, 2019

Rapid and Selective Deposition of Patterned Thin Films on Heterogeneous Substrates via Spin Coating

Source: "Rapid and Selective Deposition of Patterned Thin Films on Heterogeneous Substrates via Spin Coating" LINK

Monday, June 8, 2015

IBM Zurich present III-V on silicon wafers breakthrough technology using ALD

Template-assisted selective epitaxy of III–V nanoscale devices for co-planar heterogeneous integration with Si (Open Access)

H. Schmid, M. Borg, K. Moselund, L. Gignac, C. M. Breslin, J. Bruley, D. Cutaia and H. RielAppl. Phys. Lett. 106, 233101 (2015); http://dx.doi.org/10.1063/1.4921962

Tuesday, January 17, 2017

2nd Area Selective Deposition workshop (ASD 2017), April 20-21, 2017

Similar to last year’s successful workshop at IMEC, ASD 2017 will consist of one day of presentations and discussions. This scientific program will take place on April 21 in the city center of Eindhoven (90 minutes from Amsterdam), and will be preceded by a welcome reception at Eindhoven University on April 20. We are pleased to confirm the following invited speakers: Stacey Bent (Stanford University), John Abelson (University of Illinois at Urbana-Champaign), Rong Chen (Huazhong University), and Younghee Lee (University of Colorado at Boulder).

In addition to several invited presentations, this year’s program will include a few contributed presentations to feature recent developments in the field. The topics for these presentations will be selected based on abstracts received. Furthermore, there will be a poster session covering work related to nucleation, selective deposition, and nanopatterning. The abstract deadline is February 21. Note that this deadline is relatively tight.

The workshop is free, but registration for the scientific program and the welcome reception is mandatory. The registration deadline is April 12. Please see www.nanomanufacturing.nl/ASD2017 for more information about abstract submission and registration.

The ASD Program Committee is looking forward to your attendance.

Scott Clendenning (Intel Corporation), Annelies Delabie (IMEC), Dennis Hausmann (LAM Research), Rami Hourani (Intel Corporation), Gregory Parsons (North Carolina State University), and Adrie Mackus (Eindhoven University of Technology)

COST Action MP1402 - HERALD

Hooking together European research in Atomic Layer Deposition

Wednesday, April 19, 2023

Call for Papers on ALD & ALE Applications, at ECS Fall Meeting / Gothenburg Oct. 2023 ►►DEADLINE EXPIRES APRIL 21◄◄

The Electrochemical Society (ECS) conference is an international event running every spring and fall, and gathering 2000-4000 participants and 30-40 exhibitors both from academia and industry.

The conference has a strong focus on emerging technology and applications in both electrochemistry and solid-state science & technology.

This fall the event will be held as 244th ECS Meeting on Oct. 8-12, 2023 in Gothenburg (Sweden).

The full program as well as information on travel assistance for students can be found on https://www.electrochem.org/

The organizers of symposium G01 on “Atomic Layer Deposition & Etching Applications, 19” encourage you to submit your abstracts on the following (and closely related) topics:

1. Semiconductor CMOS applications: development and integration of ALD high-k oxides and metal electrodes with conventional and high-mobility channel materials;

2. Volatile and non-volatile memory applications: extendibility, Flash, MIM, MIS, RF capacitors, etc.;

3. Interconnects and contacts: integration of ALD films with Cu and low-k materials;

4. Fundamentals of ALD processing: reaction mechanisms, in-situ measurement, modeling, theory;

5. New precursors and delivery systems;

6. Optical and photonic applications;

7. Coating of nanoporous materials by ALD;

8. MLD and hybrid ALD/MLD;

9. ALD for energy conversion applications such as fuel cells, photovoltaics, etc.;

10. ALD for energy storage applications;

11. Productivity enhancement, scale-up and commercialization of ALD equipment and processes for rigid and flexible substrates, including roll-to-roll deposition;

12. Area-selective ALD;

13. Atomic Layer Etching (‘reverse ALD’) and related topics aiming at self-limited etching, such as atomic layer cleaning, etc.

Abstract submission

Meeting abstracts should be submitted not later than the deadline of April 21, 2023 via the ECS website: Abstract submission instruction

List of invited speakers

· Johan Swerts, (Imec, Belgium) KEYNOTE: ALD challenges and opportunities in the light of future trends in electronics

· Stephan Wege (Plasway Technology, Germany), Reactor design for combined ALD & ALE

· Masanobu Honda (TEL, Japan), Novel surface reactions in low-temperature plasma etching

· Barbara Hughes, (Forge Nano, USA), Dual Coatings, Triple the Benefit; Atomic Armor for Better Battery Performance

· Juhani Taskinen, (Applied Materials-Picosun, Finland), ALD for biomedicine

· Alex Kozen (Univ. of Maryland, USA), ALD for improved Lithium Ion Batteries

· Malachi Noked (Bar-Ilan Univ., Israel), ALD/MLD for batteries

· Yong Qin (Chinese Academy of Sciences), ALD for catalysis

· Jan Macák, (Univ. of Pardubice, Czechia), ALD on nanotubular materials and applications

· Bora Karasulu, Univ. of Warwick, UK), Atomistic Insights into Continuous and Area-Selective ALD Processes: First-principles Simulations of the Underpinning Surface Chemistry

· Ageeth Bol (Univ. Michigan, USA), ALD on 2D materials

· Pieter-Jan Wyndaele (KU Leuven-imec, Belgium), Enabling high-quality dielectric passivation on Monolayer WS2 using a sacrificial Graphene Oxide template

· Elton Graugnard (Boise State Univ., USA), Atomic Layer Processing of MoS2

· Han-Bo-Ram Lee (Incheon National Univ., Korea), Area-Selective Deposition using Homometallic Precursor Inhibitors

· Ralf Tonner (Univ. Leipzig, Germany), Ab initio approaches to area-selective deposition

· Nick Chittock (TU Eindhoven, Netherlands), Utilizing plasmas for isotropic Atomic Layer Etching

· Heeyeop Chae (Sungkyunkwan Univ., Korea), Plasma-enhanced Atomic Layer Etching for Metals and Dielectric Materials

· Charles Winter (Wayne State Univ., USA), New Precursors and Processes for the Thermal ALD of Metal Thin Films

· Anjana Devi, Ruhr Univ. Bochum, Germany), Novel precursors dedicated for Atomic Layer Processing

Visa and travel

For more information, see: www.electrochem.org/244/visa-

In addition, Mrs. Francesca Spagnuolo at the ECS (Francesca.Spagnuolo@

We are looking forward to meeting you in Gothenburg !

Sunday, December 18, 2016

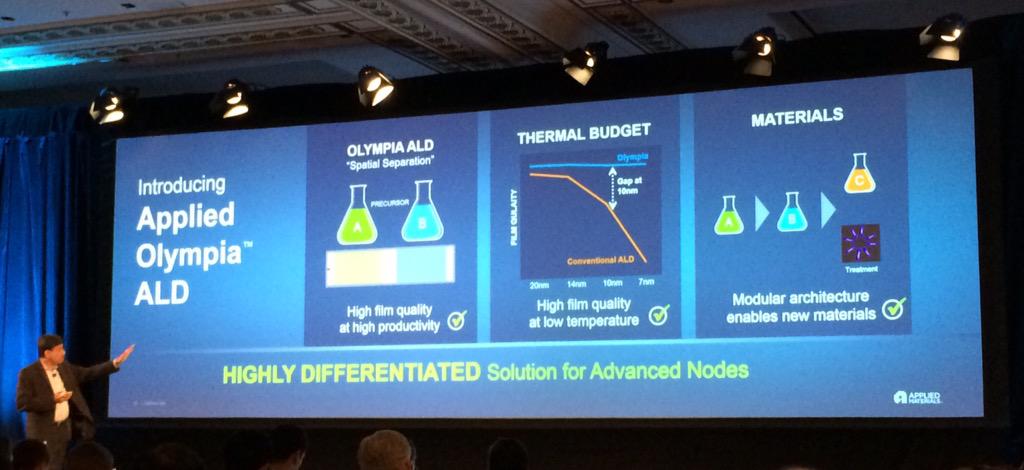

Applied Materials on Atomic Level Selective patterning technologies for 7 & 5 nm

Prabu Raja, Group VP, Patterning & Packaging group, highlights Applied Materials Centris Sym3 Etch & Olympia ALD 2015 (Applied_Blog on Twitter)

- Extreme ultraviolet (EUV) lithography

- Self-aligned octuple patterning (SAOP)

- Atomic Layer Etching (ALE)

- Selective removal

- Atomic Layer Deposition (ALD)

- Selective deposition

Applied Materials Revolutionizes Etch with Breakthrough Selective Materials Technology https://t.co/MMsqJvEBgs pic.twitter.com/zbcrneqsgi— Applied Materials (@Applied_Blog) June 29, 2016

Saturday, July 30, 2016

Wayne State presented new ALD chemistries for low temperature tantalum and selective cobalt at ALD2016

“This opens up the prospect of using tantalum in layers just a few nanometers thick as the liner for interconnect wiring in the complex geometries of next-generation electronic chips,” said the University, which worked with German chemicals giant BASF on the project accoring to Electronic Weekly.

“The Wayne State processes for tantalum and cobalt are significant steps forward in controlled growth of ultra-thin metals,” said conference chair, Dr Simon Elliott of Ireland’s Tyndall National Institute. “Strong growth is projected for area-selective deposition: in the near future, it will allow higher-precision patterning of semiconductor chips, and in the longer term it will be an enabler for manufacturing nano-structured materials on demand.” according to the same article in Electronics Weekly.

%20(1).png)