Friday, February 26, 2021

Tech Insights Teardown: Samsung’s D1z DRAM with EUV Lithography

Thursday, February 11, 2021

Imec Demonstrates 20nm Pitch Line/Space Resist Imaging with High-NA EUV Interference Lithography

Source: LINK

----------------------------

By Abhishekkumar Thakur

Thursday, January 21, 2021

Master Thesis in Nanotechnology with Alixlabs in Sweden on Atomic Level Fragmentation

Tuesday, October 6, 2020

Imec demonstrates CNT pellicle utilization on EUV scanner

LEUVEN (Belgium, LINK) October 6, 2020 — Imec, a world-leading research and innovation hub in nanoelectronics and digital technologies, announced today promising results in extreme ultraviolet (EUV) reticle protection. Multiple CNT-based pellicles were mounted on reticles and exposed in the NXE:3300 EUV scanner at imec, demonstrating the successful fabrication and scanner handling of full-field CNT-based pellicles. The tested pellicles had a single-pass EUV transmission up to 97%. The impact on imaging was found to be low and correctable based on critical dimension (CD), dose, and transmission measurements.

A pellicle is a membrane used to protect the photomask from contamination during high-volume semiconductor manufacturing. It is mounted a few millimeters above the surface of the photomask so that if particles land on the pellicle, they will be too far out of focus to print. Developing such an EUV pellicle is very challenging, since 13.5nm light is absorbed by most materials. In addition, stringent thermal, chemical, and mechanical requirements must be achieved. Such highly transparent pellicle is critical to enable high yield and throughput in advanced semiconductor manufacturing.

Imec has leveraged partners in the semiconductor industry, materials companies and fundamental research to develop an innovative EUV pellicle design with potential to survive scanner powers beyond 600 Watts

“Imec has leveraged partners in the semiconductor industry, materials companies and fundamental research to develop an innovative EUV pellicle design with potential to survive scanner powers beyond 600 Watts,” said Emily Gallagher, principal member of technical staff at imec. “We have seen tremendous progress in carbon nanotube membrane development in the past year and, based on strong collaborations with our partners, are confident it will result in a high-performance pellicle solution in the near future.”

CNTs are one-atom-thick carbon sheets rolled into tubes. The CNTs can be single-, double- or multi-walled and can vary in diameter and in length. These engineered CNTs can be arranged in different configurations to form membranes of different densities. Since 2015, imec has been working with selected CNT suppliers (Canatu Oy and Lintec of America, Inc., Nano-Science & Technology Center) to develop membranes that meet the EUV pellicle targets for properties like transmittance, thermal durability, permeability, and strength and to enable the imaging results reported today. Future work will focus on achieving acceptable lifetimes for high volume manufacturing of these pellicles in scanners.

Thursday, May 21, 2020

Reuters: Samsung Electronics builds sixth domestic contract chip-making line

Saturday, January 4, 2020

EUV - The Extreme Physics Pushing Moore’s Law to the Next Level

By Abhishekkumar Thakur

Tuesday, October 23, 2018

Imec and ASML Enter Next Stage of EUV Lithography Collaboration

Intensified collaboration will advance high-volume production with current EUV lithography and develop future EUV systems

LEUVEN (Belgium) & VELDHOVEN (The Netherlands), OCTOBER 22, 2018 (LINK) —Today, world-leading research and innovation hub in nanoelectronics and digital technologies imec, and ASML Holding N.V. (ASML), the technology and market leader in lithographic equipment, announce the next step in their extensive collaboration. Together, they will accelerate the adoption of EUV lithography for high-volume production, including the current latest available equipment for EUV (0.33 Numerical Aperture, NA). Moreover, they will explore the potential of the next-generation high-NA EUV lithography to enable printing of even smaller nanoscale devices advancing semiconductor scaling towards the post 3 nanometer Logic node. To this end, they will establish a joint high-NA EUV research lab.Imec and ASML have been conducting joint research for almost thirty years. In 2014, they created a joint research center, the Advanced Patterning Center, to optimize lithography technology for advanced CMOS integration and to prepare the ecosystem to support advance patterning requirements. Now, they bring this cooperation to the next stage with the installation of ASML’s most advanced and high-volume production dedicated EUV scanner (NXE:3400B) in imec’s cleanroom. Utilizing imec’s infrastructure and advanced technology platforms, imec and ASML researchers and partner companies can pro-actively analyze and solve technical challenges such as defects, reliability and yield, and as such accelerate the EUV technology’s industrialization.

Friday, April 27, 2018

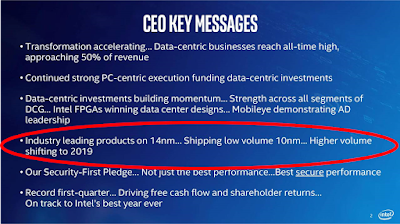

Intel shifts high volume 10 nm shipments to 2019 due to yield issues from multi-patterning

[Seeking Alpha, LINK] "We continue to make progress on our 10-nanometer process. We are shipping in low volume and yields are improving, but the rate of improvement is slower than we anticipated. As a result, volume production is moving from the second half of 2018 into 2019. We understand the yield issues and have defined improvements for them, but they will take time to implement and qualify. We have leadership products on the roadmap that continue to take advantage of 14-nanometer, with Whiskey Lake for clients and Cascade Lake for the data center coming later this year.

Moore's Law is essential to our strategy and our product leadership. It continues to create significant value for Intel and our customers. While it's taking longer and costing more to deliver and yield advanced process technologies, we are able to optimize our process and products within the node to deliver meaningful performance improvements.

For example, 14-nanometer process optimizations and architectural improvements have resulted in performance gains of more than 70% since the first 14-nanometer products were launched. We combine these advances in manufacturing technology and architecture to produce truly leadership products. And it's that product leadership that ultimately matters most to our customers and end users."

Brian M. Krzanich - Intel Corp.

Media coverage:

AnandTech

Intel Delays Broken 10nm Into 2019, Hires Jim Keller to Fix It

ExtremeTech

In-Depth-Forbes

Monday, January 22, 2018

Imec present roadmap down to 20 Ångström logic devices

Key interconnect technologies named "scaling boosters" to reach down to 2 nm may be :

- Continued scaling of self-aligned contacts

- Cobalt "Super Via" 20 nm wide

- Burried Ruthenium Rails only 10 nm wide, which seems to be a evolution of the tungsten burried Word Lines and Bitlines introduced by Qimonda for DRAM (65nm in 2009) except offcourse these rails are burried in a dielectric which will make it stackable.

Besides the interconnect technologies the presentation showed evolution from FinFETs to nanowire FETs and Imecs latest technology development in 300 mm wafer processing technology:

- Introduction of triple pattering (Much More ALD!)

- EUV Litography and the introduction Carbon Nano Tube CNT Pellicle for EUV mask protection

- Smoothening technology in patterning like Atomic Layer Etching for improving the local critical dimension uniformity (LCDU) down from 2.7 to 1.4 nm

- STTRAM - spin transfer torque magnetoresistive random-access memory

- RRAM - resistive random-access memory

- FeRAM - ferroelectric random-access memory (should be renamed DD-RAM for Dresden)

- SOTRAM - Spin Orbit Torque random-access memory

Luc Van den hove to Receive SEMI Sales and Marketing Excellence Award 👍 https://t.co/ZLjNa1xB21 @SEMIexpos #ISS2018 pic.twitter.com/ula0Oiucdh— imec (@imec_int) January 15, 2018

Saturday, November 25, 2017

The 7nm race by TSMC and Samsung - EUV or not EUV

Sales in ALD and Etch equipment have been boosted by multiple patterning technologies based on Immersion lithography, both for Logic/Foundry and Memory. Maybe as much as 1/3 of the single/multi wafer ALD equipment market is patterning related. The last two years or so analyst have been busy trying to figure out the impact on deposition and etch equipment sales if/when EUV is introduced. Here is a recent take down by Seeking Alpha (LINK). My view is that scaling is based on symbiotic use of the latest technologies and multiple patterning and EUV will co-exist and keeping the scaling path alive. In addition, scaling opens new opportunities for ALD, ALEtch and future use of selective growth technologies with atomic scale precision. According to recent reports the ALEtch market segment is now considerd an actual segment by itself and has entered HVM (LINK).

Qualcomm and Broadcom, according to the report are designing their next generation chips with TSMC’s7-nano PDK. The reason why Qualcomm went with 7nm with TSMC is the fact that the fab uses normal steppers while Samsung wants to make its 7nm with more bold and riskier EUV (Extreme Ultraviolet) photolithography technology.

View of Samsung Electronics’ Hwasung 17 line. It is expected that Samsung Electronics will build a new 7-nano plant on a nearby site according to ETNews.

Full article: Qualcomm 7nm made by TSMC [LINK]

Saturday, November 19, 2016

Why is EUV so difficult and why should we ALD people care about that

Self-aligned contact and via patterning is an established method for patterning multiple contacts or vias from a single lithographic feature. It makes use of the intersection of an enlarged feature resist mask and underlying trenches which are surrounded by a pre-patterned hardmask layer. This technique is used in DRAM cells and has been extended to patterning of active areas (see "Crossed self-aligned patterning"). It is also used for advanced logic to avoid multiple exposures of pitch-splitting contacts and vias [Wikipedia]

To inspire you even more just take time to read this excellent review by W.M.M. Kessels et al on ALD enabled pattering: "The use of atomic layer deposition in advanced nanopatterning", Nanoscale, 2014,6, 10941-10960, DOI: 10.1039/C4NR01954G. There is definitely more to come and just maybe those holes can be made by ALD as well.

Saturday, August 13, 2016

Tokyo Electron - A spacer-on-spacer scheme for self-aligned multiple patterning and integration

Saturday, May 28, 2016

Imec Tech Forum 2016 on the future of scaling, EUV and transistor architecture

Ivo Raaijmakers, chief technologist of equipment maker ASM International on scaling

An Steegen, the senior vice president of process technology at Imec on EUV and the 5 and 3 nm nodes

Saturday, March 12, 2016

Great summary of the patterning options at 7nm

Applied Materials to introduce a new system for Atomic Layer Deposition - Olympia™ ALD

Lam Research gets into the booming ALD business and doubles their install base

Jusung Engineering launches SDP R2 Revolution-Rotation ALD System at SEMICON Korea

Veeco brings low temperature nitride Spatial FAST ALD to semiconductor manufacturing

7nm Lithography Choices

Four possible scenarios for patterning the next generation of chipsMarch 7th, 2016 - By: Mark LaPedus

2. A chipmaker uses immersion/multi-patterning first. Then, EUV is inserted later in the flow where it makes sense.

3. A chipmaker inserts immersion/multi-patterning and EUV simultaneously.

4. A chipmaker uses an alternative technique, such as DSA and multi-beam.

Article: http://semiengineering.com/7nm-lithography-choices/

Sunday, March 6, 2016

ASML and IMEC EUV Progress at SPIE Advanced Lithography Conference 2016

- ASML has 8 NXE 3300 systems in the field running at ~55wph.

- ASML has shipped NXE3350B systems with ~125wph performance.

- The NXE3400B will ship this year and is expected to be the production workhorse running at ~145wph.

- The litho-etch-litho-etch-litho-etch (LE3) process prints 42nm lines with 144nm pitch and then shrinks them with a total of 27 steps.

- The SADP process creates 48nm lines on a 96nm pitch and then shrinks them with a total of 18 steps.

- EUV creates 24nm lines in an 8 step process.

Too read further about SPIE I asloo recommend this piece by Ed Korczynski at Solid State Technology looking at many additional papers presented at SPIE 2016:

http://semimd.com/blog/2016/03/03/many-mixes-to-match-litho-apps/

%20(1).png)