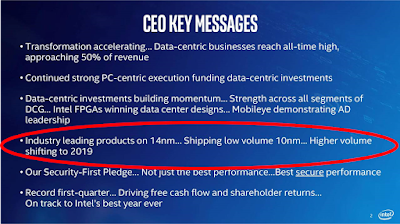

Limitless - Intel disclosed its extended roadmap to 1.4 nm process node by 2029 including back porting: One of the interesting disclosures at the IEEE International Electron Devices Meeting (IEDM) was that Intel expects to be on 2 year cadence with its manufacturing process node technology, starting with 10nm in 2019 and moving to 7 nm EUV in 2021, then 5 nm in 2023, 3 nm in 2025, 2 nm in 2027, and 1.4 nm in 2029.

In between each process node, as Intel has stated before, there will be iterative + and ++ versions of each in order to extract performance from each process node. The only exception to this is 10nm, which is already on 10+, so we will see 10++ and 10+++ in 2020 and 2021 respectively. The interesting element is the mention of back porting. This is the ability for a chip to be designed with one process node in mind, but perhaps due to delays, can be remade on an older ‘++’ version of a process node in the same timeframe.

Intel's slide with ASML's animations overlayed, as shown in the slide deck distributed by ASML. Note by Anandtech: "After some emailing back and forth, we can confirm that the slide

that Intel's partner ASML presented at the IEDM conference is actually

an altered version of what Intel presented for the September 2019

source. ASML added animations to the slide such that the bottom row of

dates correspond to specific nodes, however at the time we didn't spot

these animations (neither did it seem did the rest of the press). It

should be noted that the correlation that ASML made to exact node names

isn't so much a stretch of the imagination to piece together, however it

has been requested that we also add the original Intel slide to provide

context to what Intel is saying compared to what was presented by ASML.

Some of the wording in the article has changed to reflect this. Our

analysis is still relevant." Please see the full article in Anandtech for all the details: LINK

----------

By Abhishekkumar Thakur

%20(1).png)