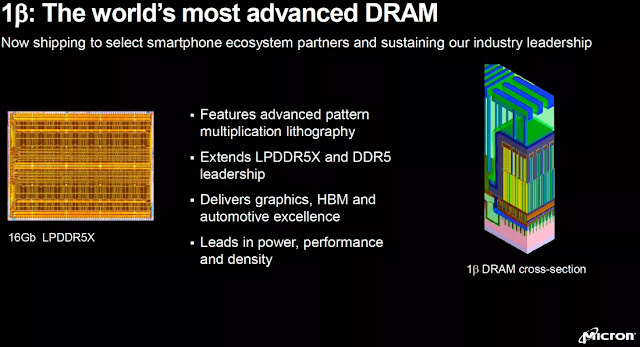

The tech landscape has seen consistent advancements, especially with the D1β (D1b) DRAM generation. Micron's D1β LPDDR5 16 Gb DRAM chips, integrated into the Apple iPhone 15 Pro, represent a significant step forward. Codenamed Y52P die, this chip offers an improved form factor and density, especially when contrasted with its LPDDR5/5X D1α 16 Gb predecessor. The integration of these chips into Apple's flagship device marks a significant design win for Micron, emphasizing the trust and partnership between the two tech giants.

In a recent teardown of the Apple iPhone 15 Pro, TechInsights has discovered a remarkable find - Micron's cutting-edge D1β LPDDR5 DRAM chips. These chips mark the industry's first foray into the D1β generation, and they are nothing short of impressive. (LINK)

Micron's technological direction is unique, especially with their decision to forego the Extreme Ultraviolet Lithography (EUVL) process, common in sub-15nm DRAM scaling. This stands in contrast to industry giants like Samsung and SK Hynix, who employ EUVL in their DRAM fabrication. Despite this, Micron has successfully launched the D1z, D1α, and D1β DRAM chips without EUVL, illustrating an alternative yet effective DRAM scaling approach.

In wrapping up, while Samsung and SK Hynix utilize EUVL in their DRAM processes, Micron has carved a different path, further solidified by their design wins with Apple. This partnership not only underscores Micron's technological prowess but also indicates the potential of varied methodologies in shaping the future of DRAM technology.

%20(1).png)