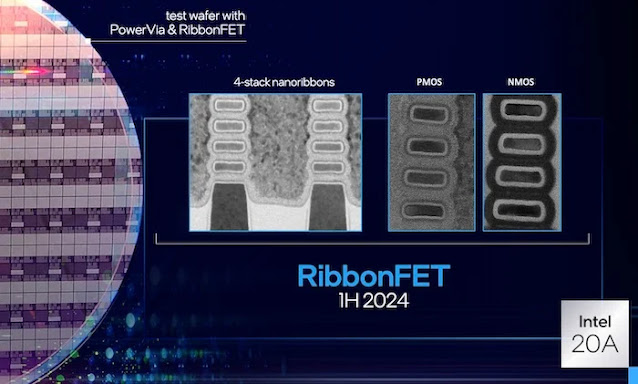

Intel Corporation / Intel Foundry has demonstrated and extensively characterized gate-all-around Silicon RibbonFET CMOS transistors with a 6 nm gate length (LG). The study showcases nanoribbon silicon thickness (Tsi) scaling down to 3 nm, enhancing short-channel effects without compromising performance. Effective workfunction engineering mitigates threshold voltage increases caused by quantum confinement at scaled Tsi, enabling reduced threshold voltage at highly scaled gate lengths. Injection velocity of 1.13x10^7 cm/s is maintained at LG=6nm without degradation down to Tsi=3 nm, highlighting advancements crucial for continued gate length scaling and the ongoing realization of Moore's Law.

Intel Foundry made groundbreaking announcements at the IEEE International Electron Devices Meeting (IEDM) 2024, showcasing advancements that propel semiconductor technology into the next decade and beyond. Highlights include innovations in transistor and interconnect scaling, advanced packaging, and emerging materials to support the industry’s roadmap toward achieving 1 trillion transistors on a chip by 2030. Intel demonstrated a 25% capacitance reduction using subtractive ruthenium for interconnections, achieved a 100x throughput improvement in advanced packaging through Selective Layer Transfer (SLT), and advanced gate-all-around (GAA) transistor scaling with Silicon RibbonFET CMOS at a 6 nm gate length. Additionally, Intel unveiled new work on gate oxide modules for scaled 2D FETs, addressing the next phase of GAA scaling.

Among the key technical breakthroughs, subtractive ruthenium stands out as a metallization alternative to copper for interconnects, offering significant capacitance reductions at tight pitches while being cost-effective and scalable for high-volume manufacturing. SLT further revolutionizes advanced packaging with ultra-fast, flexible chip-to-chip assembly, enabling smaller, higher-density chiplets for AI and other demanding applications. For transistor scaling, Intel’s demonstration of Silicon RibbonFET CMOS at 6 nm gate length delivers industry-leading short-channel effects and performance, paving the way for continued scaling under Moore’s Law. Additionally, Intel’s progress with 2D GAA NMOS and PMOS transistors and gate oxide development signals readiness for post-silicon semiconductor technologies.

Intel also highlighted progress in gallium nitride (GaN) technology, demonstrating the first 300 mm GaN-on-TRSOI substrates for high-performance power and RF electronics. These developments, alongside Intel’s continued focus on advanced memory integration, hybrid bonding, and modular system expansion, underscore its commitment to addressing challenges in AI, energy efficiency, and thermal management. With these innovations, Intel Foundry continues to lead the charge in semiconductor advancements, ensuring a robust path forward for the trillion-transistor era.

Source: Intel IEDM 2024 Innovations

%20(1).png)