ARM is evaluating CeRAM - correlated electron random access memory - technology for embedded NVM according to a recent statment from

Symetrix:

"ARM is evaluating CeRAM technology as part of its strategy in embedded nonvolatile memory offerings and their discussions with Symetrix started over three months ago. Symetrix will provide its technology and the results from Symetrix programs ongoing at the University of Texas (Dallas) and the University of Colorado (Colorado Springs) to chip foundries engaged by ARM. Other chip companies are also working with Symetrix under similar terms."

EE Times also reported on this and CeRAM technology here:

CeRAM Memory Gets ARM's Attention:

"CeRAM is based on a transition metal oxide, in this case nickel oxide (NiO). The premise is that, by cleaning up NiO through a suitable doping technique, it is possible to obtain electrically conducting NiO that can make very rapid, reversible, nonvolatile bulk transitions between its electrically insulating and conducting states. In the past, these transitions were possible only at a high pressure and temperature, but they now can be achieved at room temperature with low switching voltages and currents. Key to the operation is a reversible metal-to-insulator transition (MIT) that has its roots in the work of Sir Nevill Mott and John Hubbard. "

Here is a descriptive presentation from Symetrix that goes into detail on CeRAM and compares it to the more mainbstream ReRAM technology. In short:

1) CeRAM vs. Filament Technologies (ReRAM) according to Symetrix

• Control of material properties and proper device architecture are fundamental to this new paradigm. Evidence? No filament formation. (No electroforming)

• The CeRAM resistor is designed to exploit materials properties, surface properties, switching mechanism (endurance) and memory mechanism (retention).

• Optimizing CeRAM is a different science than building the perfect filament.

Unlike ReRAM, CeRAM is resistive memory which uses the same transition metal oxide (TMO), such as NiO, but strands are not used and electroplating. Instead CeRAM-memory quantum correlation effects observed positions of electrons, where it got its name. In the structure of the active region is allocated CeRAM TMO, which separates the two conductive layers TMO, whereas in the transition metal oxide ReRAM occupies entire domain between the metal layers.

2) CeRAM STATUS according to Symetrix:

THEORY: Confirmed with empirical results DONE

MATERIALS: Doping any TMO with any extrinsic ligand PATENTED

PROCESS: Create and isolate thin (5 nm) active region by simple spin-on or ALD PATENT FILED

ARCHITECTURE: Array only (no pass gate) PATENTED

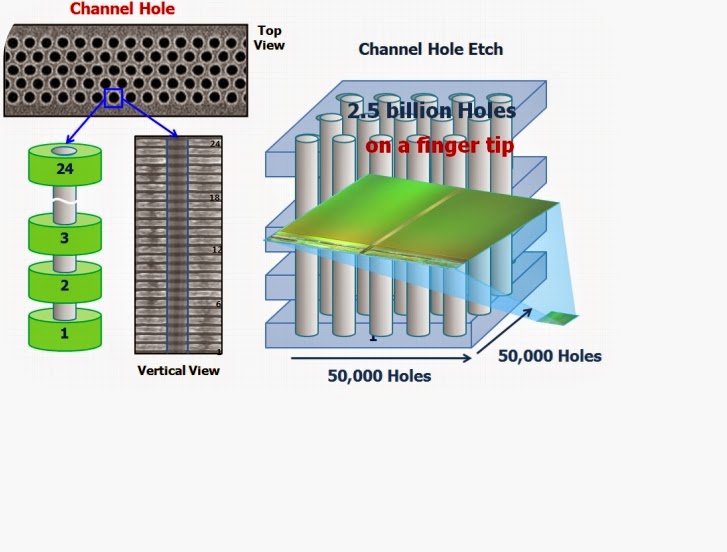

3-D (STACKING) With only silicon friendly materials IN PROCESS

FPGA Architecture PATENT FILED

Further References on CeRAM:

Patents:

16 Patents by Symetrix (as assignee) on "correlated electron memory" as returned

from Google Patent search.

Publications on CeRAM:

“A non-filamentary model for unipolar switching transition metal oxide resistance random access memories”, Kan-Hao Xue, Carlos Paz De Araujo, Jolanta Celinska, and Christopher McWilliams,

J. Appl. Phys. 109, 091602 (2011)

“Material and process optimization of correlated electron random access memories”, Jolanta Celinska, Christopher McWilliams, Carlos Paz De Araujo, and Kan-Hao Xue,

J. Appl. Phys. 109, 091603 (2011)

“Device characterization of correlated electron random access memories”, Christopher McWilliams, Jolanta Celinska, Carlos Araujo, and Kan-Hao Xue,

J. Appl. Phys. 109, 091608 (2011)

“Operating Current Reduction in Nickel Oxide Correlated Electron Random Access Memories (CeRAMs) through Controlled fabrication Processes”, Jolanta Celinska, Christopher McWilliams, Carlos Paz De Araujo, and Kan-Hao Xue,

Integrated Ferroelectrics, 124, 105-111 (2011)

“Re-Programmable Antifuse FPGA Utilizing Resistive CERAM Elements”, Christopher McWilliams, Carlos Paz De Araujo, Jolanta Celinska, and Kan-Hao Xue,

Integrated Ferroelectrics, 124, 97-104 (2011)

%20(1).png)