ALD Lab Saxony participated in the EuroCVD-Baltic ALD 2017 Conference in Linköping, Sweden 11th to 14th of June 2017. The ALD Lab Saxony members (IHM, TU Dresden), Fraunhofer ENAS and Fraunhofer IKTS) gave presentations and posters in the following fields:

- Precursors (design, synthesis and delivery)

- Process Equipment (reactors)

- Nanomaterials (particles, 2D-materials, nano structures)

- In-situ monitoring (QCM, Ellipsometry, IR, syncrotron)

- Nitrides (semiconductors, conductors, hard coatings)

- Carbides (hard coatings, semiconductors)

- Elemental films (metals, amorphous carbon)

- Emerging materials (hybrid MLD/ALD, sulfides)

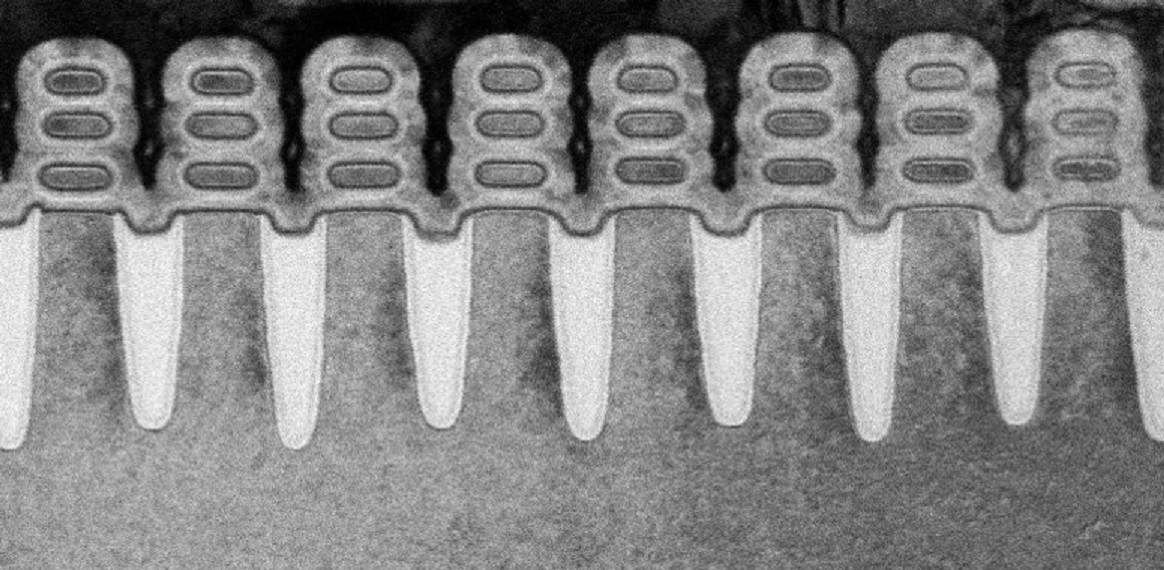

ALD Lab Saxony also took active part in the exhibition with a joint table together with Colnatec the QCM Sensor company from Arizona USA and PillarHall(TM) team from VTT Finland presenting silicon wafers and chips that enable easy analysis of thin film conformality using well-defined, record-demanding microscopic 3-D structures.

Christoph Hossbach, now at Picosun Germany (a member of ALD Lab Saxony) taking the grand stage presenting on Area Selective ALD (Photo credit: Professor Henrik Pedersen, Twitter)

Marcel Junige (TU Dresden) presenting a poster on ALD Gold precursor candidates (photo credit: Marcel Junige)

Joint exhibition table with Colnatec USA (Wendy Jameson) and VTT Finland (Photo credit: Colin Georgi)

Fraunhofer IKTS (Jonas Sundqvist) presented via video link the latest developments on Hard coatings by CVD and ALD on WC Powder (Photo Credit Jonas Sundqvist)

— Scientist Tiger (@sean_t_barry) June 14, 2017

%20(1).png)