Here are brief summary of a recent interesting article in Semiconductor Engineering by Mark LaPedus on the topic of future paths for NAND Flash Memory, which is a big market for ALD with strong competition between ASM, Lam Research and others and high aspect ration Etch Technology from Applied Materials and Lam Research. I also and added some stuff that I found elsewhere.

What’s Next For NAND?

May 19th, 2016 - By: Mark LaPedushttp://semiengineering.com/whats-next-for-nand/

Scaling standard 2DNAND technology is coming to an end and all major NAND manufacturers are ramping 3DNAND today. The NAND market leader (34%, see below) Samsung is in the lead a shipped their first 24 layer 128 gigabit chip in 2013 and have since then introduced a 32 layer are now since last year shipping the 3rd generation 48 layer chip offering a 256 gigabit storage capacity.

Intel and Micron has joined forces in NAND (joint 22% market share) and recently started shipping a 32 layer 3DNAND chip. The other duo, SanDisk (16%) and Toshiba (19%) as well as SK Hynix (10%) are trailing Samsung with their most current 48 layer chips.

Current NAND Flash Market share - Source: Semiconductor Engineering.

3DNAND Technology - Floating Gate vs. Charge Trap Flash

Floating Gate - Micron and Intel, currently uses the floating gate architecture2015 Micron Presentation explaining the advantages with their 3D NAND floating gate technology shared with Intel.

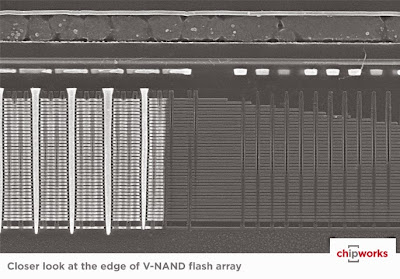

Here you can read more about the Intel/Micron floating gate technology in an article by Dick James at Chipworks. I am not sure if ALD is used for the oxide and nitride layers but it is a possibility for sure due to high aspect ratio sttructures..

Charge Trap - Samsung, SK Hynix and the SanDisk/Toshiba are all steaming up the layers using charge trap NAND.

Samsung Promo video: Samsung's 3D V-NAND flash memory is fabricated using an innovative

vertical design. Its vertical architecture stacks 32 cell layers on top

of one another, rather than trying to decrease the cells' length and

width to fit today's ever-shrinking form factors. [youtube.com]

A Look Ahead at IEDM 2015, Solid State Technology, By Dick James, Senior Technology Analyst, Chipworks

Many available cross sections of available on the internet show high-k material (Al2O3) and a metal nitride (TiN) gate being used for the to connect to the tungsten control gate. I can only assess it as ALD being used in these extreme aspect ratios.

According to a statement in the article made by Applied materials 3DNAND will make the step from 48 to 64 layers in 2016 and if it can be scaled further will be limited at some point by high aspect ration etch capability of 96 or 128 layers. However, I am a bit doubtful here that actually the technology will be limited by etch unit process engineers. As a comparison, many think that deep trench DRAM scaling was killed by high aspect ratio etch but it was not, it was rather the impossibility to scale the memory cell down from 8F2 , via 6F2 down ti a most compact 4F2 cell design. In any, case these are not extreme aspect ratios for ALD so either the etchers or the device physics will have to throw in the towel for 3DNAND momentarily. - to conclude there are two possible paths according to Mark LaPedus:

The first path:

"So going forward, NAND suppliers will simultaneously follow two parallel paths. The first path is to wait for the etch tools and other manufacturing techniques to arrive. And if they arrive on time, vendors could scale today’s 3D NAND device from 32- and 48-layers, to 64 layers, to 96 and then to 128."

The second path:

"The second path is to move towards string stacking technology. This involves stacking two or more individual devices on top each other. Each device is separated by an insulating layer. String stacking is already in the works. Recently, Micron presented a paper on a new 64-layer chip. Micron, according to multiple sources, stacked two 32-layer chips on top of each other. In theory, string stacking could involve several different combinations. For example, a vendor could stack three 32-layer chips, enabling a 96-layer device. In addition, a vendor could stack three 96-layer chips, resulting in a 288-layer product."

%20(1).png)