Here is quite promising results on fabricating ALD TiO2 high-efficiency monolithic perovskite/Si tandem cells in a joint collaboration between California Institute of Technology, USA, and The Australian National University, Canberra, and Flinders University, Adelaide,in Australia.

In situ recombination junction between p-Si and TiO2 enables high-efficiency monolithic perovskite/Si tandem cells

Heping Shen, Stefan T. Omelchenko, Daniel A. Jacobs, Sisir Yalamanchili, Yimao Wan, Di Yan, Pheng Phang, The Duong, Yiliang Wu, Yanting Yin, Christian Samundsett, Jun Peng, Nandi Wu, Thomas P. White, Gunther G. Andersson, Nathan S. Lewis and Kylie R. Catchpole

Distributed under a Creative Commons Attribution NonCommercial License 4.0 (CC BY-NC).

[Abstract] Increasing the power conversion efficiency of silicon (Si) photovoltaics is a key enabler for continued reductions in the cost of solar electricity. Here, we describe a two-terminal perovskite/Si tandem design that increases the Si cell’s output in the simplest possible manner: by placing a perovskite cell directly on top of the Si bottom cell. The advantageous omission of a conventional interlayer eliminates both optical losses and processing steps and is enabled by the low contact resistivity attainable between n-type TiO2 and Si, established here using atomic layer deposition. We fabricated proof-of-concept perovskite/Si tandems on both homojunction and passivating contact heterojunction Si cells to demonstrate the broad applicability of the interlayer-free concept. Stabilized efficiencies of 22.9 and 24.1% were obtained for the homojunction and passivating contact heterojunction tandems, respectively, which could be readily improved by reducing optical losses elsewhere in the device. This work highlights the potential of emerging perovskite photovoltaics to enable low-cost, high-efficiency tandem devices through straightforward integration with commercially relevant Si solar cells.

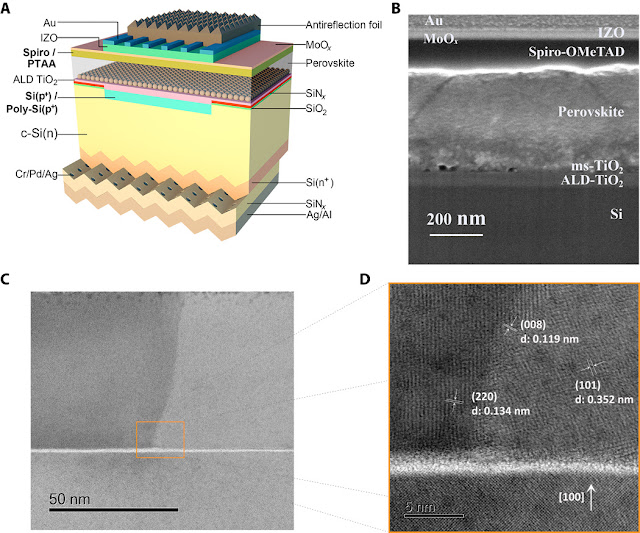

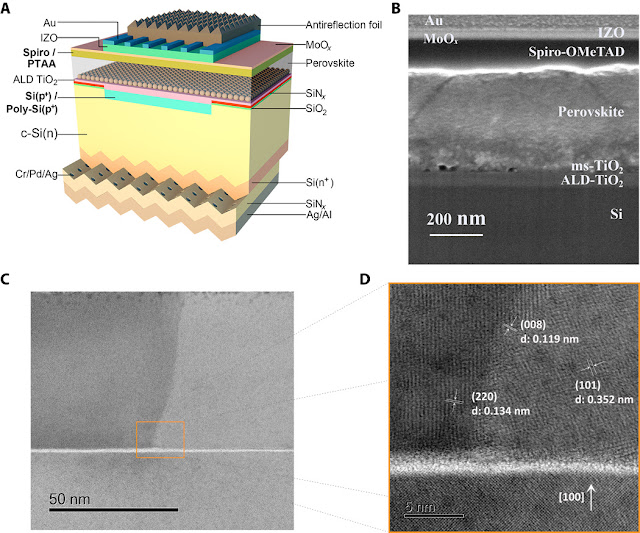

Schematic illustration and morphological characterizations of the interlayer-free monolithic perovskite/Si tandem solar cell : (A) Schematic of the interlayer-free monolithic perovskite/crystalline-silicon (c-Si) tandem solar cell (not to scale). Initial tests were carried out on homojunction Si cells with Spiro-OMeTAD (Spiro) as the top perovskite contact; however, our best performance was obtained with polysilicon (poly-Si) bottom cells and PTAA {poly[bis(4-phenyl)(2,4,6-trimethylphenyl)amine]} as the top hole-selective layer. (B) Cross-sectional SEM image of the tandem device based on a Si homojunction subcell from the top surface to the p+-Si layer [Spiro-OMeTAD is used as a hole transport material (HTM)]. The antireflection layer was not included because of the large thickness of ~1 mm. (C) Scanning transmission electron microscopy (STEM) bright-field (BF) image, and (D) high-resolution STEM BF image of the TiO2/p+-Si interface.

The TiO2 layers prepared using different ALD precursors and ALD systems yielded markedly mutually different J-V characteristics in our TiO2/p+-Si test structures (below).

- Ohmic, highly conductive behavior between TiO2 and p+-Si was observed in samples with TiO2 prepared using tetrakisdimethylamidotitanium (TDMAT) as the ALD precursor (green solid line)

- Very low conductivity (ρ > 10 ohm·cm2) in the low-bias region was obtained when using titanium tetrachloride (TiCl4) instead (blue solid line)

- Titanium tetraisopropoxide (TTIP) resulted in intermediate performance, displaying conductive but distinctly nonlinear J-V behavior (yellow solid line).

The ALD processing was conducted in two different ALD reactors:

- TDMAT process : Ultratech Fiji 200 Plasma ALD system (now Veeco CNT)

- TiCl4 process : BENEQ TFS200

- TTIP process : BENEQ TFS200

Contact behavior and simulated band diagram of TiO2/p+-Si interfaces. (A) Schematic of the structure used for measuring contact resistivity. (B) Comparison of the J-V behavior of ITO/p+-Si and various TiO2/p+-Si structures before and after annealing at 400°C in air. TiCl4-ALD TiO2 listed here is deposited with a reactor chamber temperature of 75°C. (C) Simulated band diagram of the TiO2/p+-Si at equilibrium assuming n-type doping of 5 × 1018 cm−3 on TiO2 and 1019 cm−3 for p+-Si (appropriate for our test structure with TDMAT TiO2; see table S3). The unknown interfacial energy gap Δ is shown here for illustrative purposes as 600 meV, which falls within the range of reported measurements (31). Both mechanisms of direct- and tunneling-assisted capture by interfacial density of states (DoS) are shown.

The Australian-Californian team conclude :

- Successful demonstration of two proof-of-concept 2-T perovskite/Si tandem devices that function without a conventional interlayer between their subcells.

- fabrication of an nc-Si tunnel junction interconnect is relatively straightforward for HIT cells, these layers introduce a small but potentially important amount of parasitic loss in the region of ~550 to 700 nm (16), where the nc-Si is absorbing and the perovskite top cell’s absorption is simultaneously incomplete.

- The publication of a similar scheme using SnO2 (40) instead of TiO2 while this paper was under review demonstrates the wide applicability of the interlayer-free concept. Jointly, our work highlights the potential of emerging perovskite photovoltaics to enable low-cost, high-efficiency tandem devices through straightforward integration with commercially relevant and emerging Si solar cells.

%20(1).png)