Semiwiki Tom Dillinger reports on an interesting paper by TSMC at the recent IEDM 2021 conference in San Francisco using selective ALD with the help of SAMs or Dielectric on Dielectric (DOD) as it is called.

From the article sumary: Continued interconnect scaling below the 3nm node will necessitate unique process development research to maintain electrical and reliability specs in the presence of (up to 4nm) overlay error. The need for low-K interlevel dielectrics is a given – yet, the via etch in these materials is not especially tolerant of EPE.

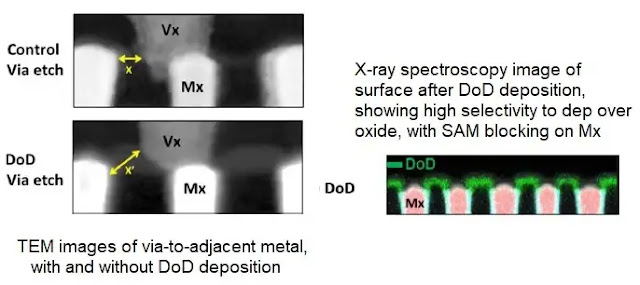

TSMC has demonstrated a potential process flow for a “self-aligned via” with an additional DoD material. The etch rate differential of the DoD results in more robust via-to-adjacent metal reliability. This process flow utilizes two unique steps – the SAM of a blocking material on metal surfaces, and the selective ALD of a dielectric-on-dielectric.

%20(1).png)

I saw some testimonies about this herbal specialist called @drmosesbuba and decided to email him so I gave his herbal product a try. i emailed him and he get back to me and we discussed, he gave me some comforting words and encouraged me also and then gave me his herbs and cream for Penis Enlargement Within 1 week of it, i began to feel the enlargement of my penis, " and now it just 2 weeks of using his products my penis is about 10 inches longer and am so happy today. Contact @drmosesbuba for any problem via WhatsApp +2349060529305 or email buba.herbalmiraclemedicine@gmail.com

ReplyDeleteThanks doctor Moses