Researches at Imec/KU Leuven show that MOF-CVD ZIF films demonstrate dielectric and mechanical characteristics competitive with state-of-the-art porous OSG dielectrics (a

low-k organosilicate glass). They also argue that the MOF-CVD integration process may outperform porous OSG dielectrics in future integration schemes because of the gap-filling nature of the deposition process. Please check details below as well as quite some good stuff available in the

Supplementary Information

Vapor-deposited zeolitic imidazolate frameworks as gap-filling ultra-low-k dielectrics (Open Access)

Mikhail Krishtab, Ivo Stassen, Timothée Stassin, Alexander John Cruz, Oguzhan Orkut Okudur, Silvia Armini, Chris Wilson, Stefan De Gendt & Rob Ameloot

Nature Communications volume 10, Article number: 3729 (2019) DOI

https://doi.org/10.1038/s41467-019-11703-x

Abstract: The performance of modern chips is strongly related to the multi-layer interconnect structure that interfaces the semiconductor layer with the outside world. The resulting demand to continuously reduce the k-value of the dielectric in these interconnects creates multiple integration challenges and encourages the search for novel materials. Here we report a strategy for the integration of metal-organic frameworks (MOFs) as gap-filling low-k dielectrics in advanced on-chip interconnects. The method relies on the selective conversion of purpose-grown or native metal-oxide films on the metal interconnect lines into MOFs by exposure to organic linker vapor. The proposed strategy is validated for thin films of the zeolitic imidazolate frameworks ZIF-8 and ZIF-67, formed in 2-methylimidazole vapor from ALD ZnO and native CoOx, respectively. Both materials show a Young’s modulus and dielectric constant comparable to state-of-the-art porous organosilica dielectrics. Moreover, the fast nucleation and volume expansion accompanying the oxide-to-MOF conversion enable uniform growth and gap-filling of narrow trenches, as demonstrated for 45 nm half-pitch fork-fork capacitors.

The preparation method is described in detail in the paper and includes a number of PVD, ALD and CVD process steps as follows:

Preparation of MOF-CVD precursor layers on blanket wafer

The layers of ALD ZnO and PVD Co were prepared on highly-doped p

++ Si substrates. ALD ZnO deposition was realized at 120 °C by 30 cycles of diethyl zinc (DEZ)/water precursor pulses separated by N

2 purge steps (Savannah S200, Veeco Instruments Inc.). PVD Co film was sputtered on Ar-plasma precleaned Si substrate (NC7900, Canon Anelva Corp.).

Preparation of MOF-CVD precursor layer on patterned wafer

The fork–fork capacitor structures featuring 45 nm line/space width were prepared on p-type 300 mm Si-wafers according to a modified integration route (Supplementary Fig.

2) based on using sacrificial amorphous carbon (a-C) layer to form a pattern of passivated copper wires. The initial stack of layers above the substrate consisted of 1000 nm SiO

x, 30 nm SiCN diffusion barrier, 90 nm a-C, and a multilayer hard-mask stack. After formation of a device pattern in the top positive resist coating with 193 nm immersion lithography, the pattern features were then transferred into the underlying a-C film. Following the wet removal of hard-mask residues, the exposed surfaces of a-C/SiCN were coated with 3 nm ALD TiN. The subsequent metallization steps included sputtering of 20 nm Cu seed, electroplating of 500 nm Cu, and chemical mechanical polishing down to the a-C film. The removal of a-C sacrificial layer was done in He/H

2 remote plasma. Afterward, the metallic lines were passivated with a non-conformal 3 nm PECVD SiCN barrier layer and then additionally covered with a conformal 2 nm PEALD SiN

x film. The deposition of CVD Co was realized at 200 °C on VECTOR Excel tool cluster (Lam Research Corp.). Before deposition of CVD Co on the SiCN/SiN

x-passivated Cu pattern, the growth conditions were optimized on blanket SiN

x surface to obtain 4.0 ± 1.0 nm Co layer across 300 mm wafer (assessed by RBS). ALD ZnO deposition on the metal lines passivated with SiN

x layer was performed by applying the same growth conditions as used on blanket wafers (see above).

Vapor-phase conversion process (MOF-CVD)

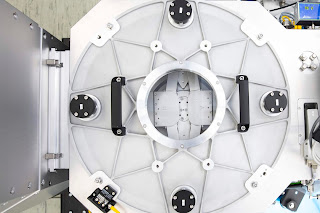

For the conversion to appropriate ZIF layer, samples with precursor layers were placed in a glassware reactor (Supplementary Fig.

1). The glassware reactor was connected to a vacuum pump via a manual valve. Upon assembly the reactor was checked for leaks. The glass tube containing 2-methylimidazole powder (99%, CAS #693-98-1, Sigma-Aldrich) was connected to one of the ports of the glassware reactor via another manual valve. The whole setup was placed in a furnace preheated at 120 °C. After the temperature stabilization (15 min), the valve to the vacuum pump was opened, and the reactor was evacuated until pressure stabilization below 10 mbar. The vacuum valve was then closed and the valve to the 2-methylimidazole tube opened. The exposure of samples to vapors of 2-methylimidazole was set to 120 min, after which the precursor valve was closed, and the sample area of the reactor was kept under dynamic vacuum for 15 min to remove the unreacted organic linker from the sample surface and pores of formed ZIF films (activation). Finally, the reactor was let to cool down before the samples could be taken out for further characterization.

Two proposed routes for the integration of ultra-low-k MOF dielectrics in on-chip interconnects via the MOF-CVD process. Routes A and B differ in how the MOF precursor layer is formed around the interconnect wires. In Route A, metal oxide to be converted into MOF is deposited after passivation of metal lines, while Route B relies on selective conversion of metal oxide formed through controlled oxidation of the metal pattern From: Vapor-deposited zeolitic imidazolate frameworks as gap-filling ultra-low-k dielectrics

Validation of the MOF-CVD process and characterization of the deposited MOF thin films. a Schematic representation of the conversion of ALD ZnO and native CoOx to ZIF-8 and ZIF-67 and the corresponding increase in thickness as measured by spectroscopic ellipsometry (SE) and from SEM cross-sectional images. b Baseline-corrected GI-XRD diffraction patterns together with simulated powder diffractogram for ZIF-8. c Ellipsometric porosimetry with methanol and water as adsorbates. The amount of adsorbate corresponds to the change of the ellipsometric angle Delta (@633 nm) relative to the value recorded before introducing probe molecules. The values are normalized against the Delta change measured at methanol saturation pressure. d AFM topography images of MOF-CVD films: ZIF-8 (purple frame) and ZIF-67 (light blue frame) From: Vapor-deposited zeolitic imidazolate frameworks as gap-filling ultra-low-k dielectrics

Open Access This article is licensed under a Creative Commons Attribution 4.0 International License, which permits use, sharing, adaptation, distribution and reproduction in any medium or format, as long as you give appropriate credit to the original author(s) and the source, provide a link to the Creative Commons license, and indicate if changes were made. The images or other third party material in this article are included in the article’s Creative Commons license, unless indicated otherwise in a credit line to the material. If material is not included in the article’s Creative Commons license and your intended use is not permitted by statutory regulation or exceeds the permitted use, you will need to obtain permission directly from the copyright holder. To view a copy of this license, visit

http://creativecommons.org/licenses/by/4.0/.

%20(1).png)