Thursday, January 21, 2021

Master Thesis in Nanotechnology with Alixlabs in Sweden on Atomic Level Fragmentation

Tuesday, January 19, 2021

Webinar - Enhancing Yield by Minimizing Contamination with Beneq ALD coating solutions

- Common issues of metal or particle contamination on critical chamber components

- Common coating methods against corrosion, and how they compare

- What properties to look for e.g. purity, uniformity, when evaluating the optimal protective coating solution

- Unique benefits of ALD coatings with Al2O3 and Y2O3

- Working with your OEM partner to design, test and implement an ALD coating solution for your equipment

Atomic Layer Deposition of 2D Metal Dichalcogenides for Electronics, Catalysis, Energy Storage, and Beyond

Monday, January 18, 2021

RASIRC Granted Taiwan Patent for Method and Systems for Purifying Hydrogen Peroxide Solutions

Innovative new products that purify and deliver ultra-pure oxidation chemistries

Related RASIRC Products

Tuesday, January 12, 2021

Semiconductor Materials $50B Market on a Strong Run in 2021

Picosun ALD reactors installed in Africa's first ALD-Lab at University of Johannesburg RSA

Thursday, January 7, 2021

How ALD can be used to stack 2D materials on one another at a nanometer scale

Surface ligand removal in atomic layer deposition of GaN using triethylgallium

Tuesday, December 22, 2020

Nanoscale lithography of metal–organic frameworks (MOFs)

Friday, December 18, 2020

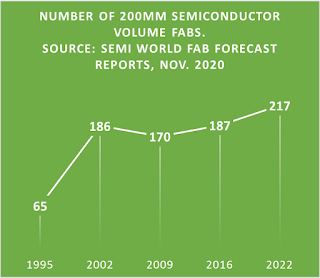

The 200 mm Wafer Processing Equipment market is surging - who´s there fore ALD?

- Arradiance : LINK

- Beijing NAURA Microelectronics Equipment Co.,Ltd. : LINK

- Beneq : LINK

- Encapsulix SA : LINK

- Forge Nano (Sundew Technologies) : LINK

- FHR Anlagenbau GmbH : LINK

- Isac Research : LINK

- KE Micro : LINK

- Korea Vacuum Tech, Ltd. (KVT) : LINK

- Kurt J Lesker : LINK

- NCD : LINK

- Oxford Instruments : LINK

- Picosun Oy : LINK

- Plasma Therm : LINK

- Sentech : LINK

- Sundew Technologies : LINK

- SUPERALD : LINK

- SVT Associates : LINK

- Trion Technology : LINK

- Veeco CNT : LINK

- Wuxi MNT Micro and Nanotech : LINK

- ZLD Technology : LINK

Imec demonstrate BEOL compatible architecture that paves the way to high-density 3D-DRAM memories

Prodrive Technologies launch Bias generator with shaped waveform for Atomic Layer Processing

Nanexa AB signs USD 3 million Investment Agreement with Applied Materials to scale-up GMP production site for ALD-coated pharmaceuticals

Thursday, December 17, 2020

EU Signs €145bn Declaration to Develop Next Gen Processors and 2nm Technology

- Globalfoundries Fab1 in Dresden Germany

- STMicro Corlles in Grenoble France

- Infineon Dresden, Germany

- Infineon Villach, Austria

- Bosch Sensortech Dresden, Germany

- Intel Leixlip,

Low Resistivity Titanium Nitride Thin Films ALD realized by RASIRC Brute® Hydrazine vaporization technology

- Relatively cheap precursor, mainly TiCl4 and TDMAT, as compared to the much more expensive precursors with lower vapor pressure for tantalum metal nitrides (PDMAT) and metals like Co (CCTBA) and Ru (RuCp´s).

- High vapor pressure and reactivity allowing fast conformal processing bay both CVD, pulsed CVD and ALD for TiCl4/NH3 based processes

- Possibility to tune low resistivity films however at relatively high temperatures (TiCl4/NH3) not allowing for BEOL thermal budget requirements (<390 °C)

- Excellent barrier properties hindering metal diffusion (TDMAT and TiCl4)

- Metal gate work function tuning by doping and partial controlled oxidation

- Oxygen gettering driving excess oxygen from the gate oxide channel interface into the metal gate reducing the CMOS device EOT.

- Mini Batch and Large Batch processing capability (e.g. TEL Indy, ASM A412, Kokusai ALDina, Picosun Sprinter)

Due to low resistivity, titanium nitride (TiN) thin films are in production as the diffusion barrier for Cu, Co and W as well as the gate metal barrier in CMOS. However, as mentioned, for high aspect ratio features, thermal ALD deposition is needed because of high conformality. Therefore, it is very important to develop thermal ALD TiN processes further to improve the capacitor electrode, barrier and CMOS metal gate properties to perfection.

Cheng-Hsuan

Kuo and co-workers at UCSanDiego in the Kummel research group, has recently concluded a study on TiN ALD utilizing the RASIRC BruteÒ Hydrazine (N2H2) vaporizer technology, which is

presented this week at IEEE SISC December 16-18 (LINK).

In the work, titanium tetrachloride (TiCl4) and anhydrous hydrazine (Rasirc, Brute HydrazineÒ) were employed as the precursors with ultra-high purity nitrogen purge gas.

- The TiN ALD chamber was connected to an in-vacuo Auger Electron Spectrometer (RBD Instruments), which was used to determine the atomic composition of ALD. (Fig. 1)

- The sample was biased at -100V DC and Ar plasma (50W) was used to remove the surface oxides and impurities. (Fig. 2)

- To determine resistivity, four-point probe (Ossila) measurements were performed on TiN thin films on degreased SiO2 substrates. (Fig. 3)

- Scanning electron microscopy (SEM), ellipsometry, and X-ray reflectivity (XRR) were used to measure TiN film thicknesses. (Fig. 4)

To conclude, these experiments indicate that minimizing oxygen concentration is key in producing TiN thin films with desirable electrical properties.

The optimal resistivity of the TiN deposited at 350oC was 160 micro-ohm-cm which is the lowest reported resistivity of any TiN film deposited by thermal ALD. As stated above the importance of 3D process capability can be met by having TiN thin films synthesized by using thermal ALD and post-plasma treatment reducing oxygen concentration and impurities potentially in very high aspect ratio structures such as contact holes, FinFET, Gate all around FETs, vias, DRAM capacitors structures as well as 3DNAND metal gates and contacts.

References

[1] C. H.

Ahn. et al. Metals and Materials International, 7 (2001)

[2] Steven

Wolf et al. Applied Surface Science 462 (2018)

Acknowledgements

This work

was supported in part by the SRC

LINKS

EEE SISC December 16-18 (LINK).

Beneq completes new clean room facility

Built with the latest cleanroom design and construction technology, the new facility adds approximately 350 square meters of ISO 7 cleanroom floor space at Beneq's headquarters. It will be used for product and process development, equipment assembly, prototyping, and testing services.

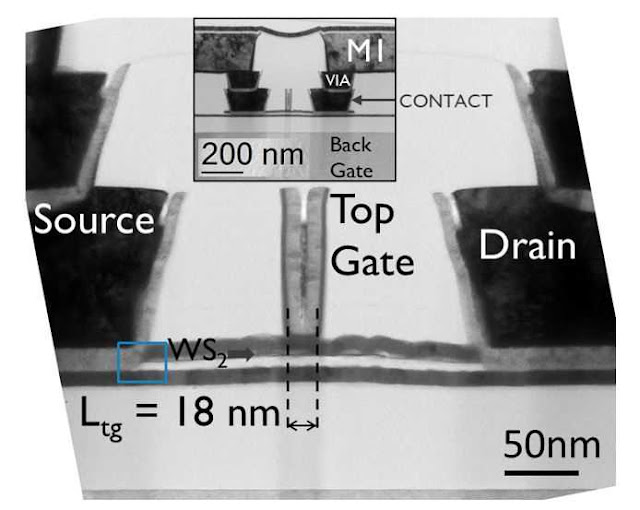

Imec introduces 2D materials in the logic device scaling roadmap

More details can be found in 4 papers presented at the 2020 IEDM conference:

[1] ‘Introducing 2D-FETs in device scaling roadmap using DTCO’, Z. Ahmed et al.

[2] ‘Wafer-scale integration of double gated WS2-transistors in 300mm Si CMOS fab’, I. Asselberghs et al.

[3] ‘Dual gate synthetic WS2 MOSFETs with 120µS/µm Gm 2.7µF/cm2 capacitance and ambipolar channel’, D. Lin et al.

[4] ‘Sources of variability in scaled MoS2 FETs’, Q. Smets et al. (IEDM highlight paper)

Friday, December 11, 2020

KLA Introduces Two New Systems that Take On Semiconductor Manufacturing's Toughest Problems

Thursday, December 10, 2020

ALD Webinar - The Ultimate Anti-Corrosion Coating Solution presented by Beneq

- Common issues of metal or particle contamination for critical chamber components

- Common coating methods to protect against corrosion, and how they compare

- What properties to look for – e.g. high purity and uniformity – when evaluating the optimal protective coating solution

- Unique benefits of ALD coatings with Al2O3 and Y2O3

- How to work with your OEM partner to design, test and implement an ALD coating solution for your equipment

Agenda and Speaker Information

Sponsored by

[PALD] SUMMIT Video Library is now available on demand - Enjoy!

The 2nd [PALD] Summit by Forge Nano is now happening. This is following the first very successful event earlier in 200 and Forge Nano is planning yet a 3rd event i summer 2021. More information will come in the near future.

Anyhow, the [PALD] SUMMIT Video Library is now available on demand - Enjoy!

------ [PALD] SUMMIT on Demand LINK ------

Presentation by BALD Engineering during the first [PALD] Summit

%20(1).png)