Combination of thermal and plasma ALD, single wafer or batch processing, and a unique preheating module maximize options for flexible volume production

25 September, 2019, Grenoble, France – Beneq, a leading provider of ALD R&D and production technology, today announced the BENEQ TransformTM, a versatile ALD platform dedicated to More-than-Moore device fabrication.

The brand-new cluster design offers customers unparalleled flexibility by combining both thermal and plasma ALD with single wafer and batch processing, on a single automated platform. Fully compliant with industry quality and SEMI standards the BENEQ TransformTM is a one-stop ALD solution for Power Electronics, MEMS and Sensors, RF, LED, Photonics, and Advanced Packaging applications.

“Among hundreds of application requests brought to us by customers today, we are most excited by GaN devices for RF and Power applications as well as Photonics, both III-V and Silicon,” said Dr. Patrick Rabinzohn, Beneq’s Semiconductor Business Executive. “In particular surface passivation, gate dielectrics, nucleation layers and encapsulation layers are all well addressed with the BENEQ TransformTM.”

The brand-new cluster design offers customers unparalleled flexibility by combining both thermal and plasma ALD with single wafer and batch processing, on a single automated platform. Fully compliant with industry quality and SEMI standards the BENEQ TransformTM is a one-stop ALD solution for Power Electronics, MEMS and Sensors, RF, LED, Photonics, and Advanced Packaging applications.

“Among hundreds of application requests brought to us by customers today, we are most excited by GaN devices for RF and Power applications as well as Photonics, both III-V and Silicon,” said Dr. Patrick Rabinzohn, Beneq’s Semiconductor Business Executive. “In particular surface passivation, gate dielectrics, nucleation layers and encapsulation layers are all well addressed with the BENEQ TransformTM.”

Truly Versatile

More than Moore (MtM) applications are evolving at a phenomenal pace. To be competitive manufacturers are adopting advanced thin film technologies. Often, they need to combine surface preparation, interfacial layer and functional layer deposition sequences - all in one tool.

Currently available ALD production systems offer only one type of ALD process - either thermal or plasma enhanced. This creates the need for a versatile tool that supports multiple deposition capabilities.

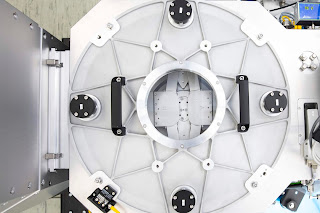

The BENEQ TransformTM confidently combines thermal and plasma ALD processing, on a single wafer or in batches, while easily configurable. It is capable of surface pre-treatment and can coat substrate materials at wafer sizes from 3 to 8 inches.

It works well for R&D, prototyping, as well as volume production. With the BENEQ TransformTM customers now have the option to run several different ALD processes on multiple devices and applications, all on a single footprint!

The most complete configuration offers two ALD process modules, pre-heating station, surface plasma treatment and wafer cooling.

Currently available ALD production systems offer only one type of ALD process - either thermal or plasma enhanced. This creates the need for a versatile tool that supports multiple deposition capabilities.

The BENEQ TransformTM confidently combines thermal and plasma ALD processing, on a single wafer or in batches, while easily configurable. It is capable of surface pre-treatment and can coat substrate materials at wafer sizes from 3 to 8 inches.

It works well for R&D, prototyping, as well as volume production. With the BENEQ TransformTM customers now have the option to run several different ALD processes on multiple devices and applications, all on a single footprint!

The most complete configuration offers two ALD process modules, pre-heating station, surface plasma treatment and wafer cooling.

Designed for the Fab

Unlike ALD production platforms featuring vertical flip functions, the TransformTM loads wafers in a horizontal position and seamlessly integrates with the rest of your production line. Such a loading mechanism is also proven to minimize handling issues, and particle generation associated with non-standard cassette batch loading systems.

The BENEQ TransformTM features a proprietary preheating module that eliminates hours of waiting time and boosts throughput to a whole new level (15 wph @50 nm Al2O3, in thermal mode). Throughput can be further increased by adding up to 2 more process modules, thermal or plasma.

The BENEQ TransformTM produces a wide range of oxides including Al2O3, HfO2, Ta2O5, TiO2, and SiO2, and nitrides such as AIN and TiN. What sets the TransformTM apart from other tools is its ability to scale up throughput and maintain the same uniformity regardless of the temperature, e.g. >400°C.

The BENEQ TransformTM features a proprietary preheating module that eliminates hours of waiting time and boosts throughput to a whole new level (15 wph @50 nm Al2O3, in thermal mode). Throughput can be further increased by adding up to 2 more process modules, thermal or plasma.

The BENEQ TransformTM produces a wide range of oxides including Al2O3, HfO2, Ta2O5, TiO2, and SiO2, and nitrides such as AIN and TiN. What sets the TransformTM apart from other tools is its ability to scale up throughput and maintain the same uniformity regardless of the temperature, e.g. >400°C.

SEMI Certified

The BENEQ TransformTM shortens cycle time and speeds up fab adaptation by implementing SECS/GEM standards. It is fully compliant with SEMI S2/S8 for environmental, ergonomics and safe operations.

To learn more, visit www.beneq.com/transform.

To learn more, visit www.beneq.com/transform.

About Beneq

Beneq is the home of ALD, offering a wide portfolio of equipment products and development services. Today Beneq leads the market with innovative solutions for flexible high-volume manufacturing (BENEQ TransformTM), advanced R&D (TFS 200, R2), ultra-fast high precision spatial ALD coatings (C2R), roll-to-roll thin film coating of continuous webs (WCS 600), and specialized batch production for thicker film stacks (P400, P800). Headquartered in Espoo, Finland Beneq is dedicated to making ALD technology accessible for researchers and providing the invisible advantage in emerging semiconductor applications.

Press Contact

Lie Luo

Beneq

lie.luo@beneq.com

Press Contact

Lie Luo

Beneq

lie.luo@beneq.com

%20(1).png)

Lecture, part I

Lecture, part I Lecture, part II

Lecture, part II