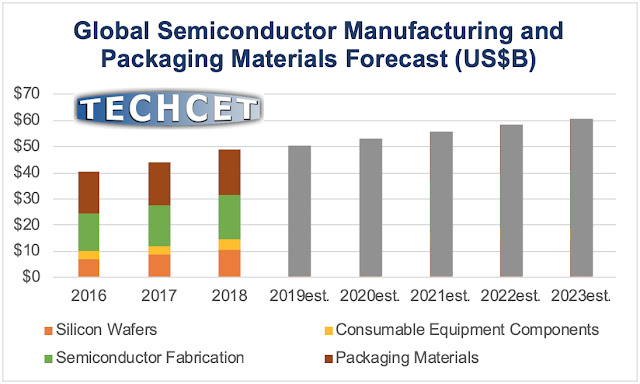

TECHCET-the

electronic materials advisory services firm providing business and

technology information- announced that global revenues for semiconductor

manufacturing and packaging materials are expected to grow 3.1%

year-over-year (YoY) in 2019 to US$50.4B, of which 58% represents

semiconductor fab materials. Steadily increasing demand for memory chips

in 2018 lifted total materials market revenues to US$48.9B in 2018,

while the compound annual growth rate (CAGR) through 2023 is forecast at

4.3% as detailed in the latest TECHCET Critical Materials Reports (CMR)

and shown in the attached figure.

Global

trade issues in 2018 run the risk of devolving into real trade wars, if

governments and companies do not negotiate business terms from a place a

mutual respect. "Wars can only have winners and losers," reminded Lita

Shon-Roy, TECHCET President and CEO. "While issues can have win-win

resolutions after mutually-respectful negotiations."

At the 2018 Critical Materials Council (CMC) Seminar, held last October in Ningbo, China in coordination with China's IC Materials Technology Innovation Alliance (ICMtia), representatives of global chip-makers including Intel, GlobalFoundries, and Texas Instruments discussed ways to ensure electronic materials supply-chain robustness in an era of short-sighted protectionist tariffs. All three companies have high-volume manufacturing (HVM) fabs in mainland China along with the US, and all need to source a wide range of specialty materials from global suppliers.

During private face-to-face meetings between CMC fab members in Ningbo, held just after the public CMC Seminar, ON Semiconductor shared that they have a plan prepared to deal with tariffs goings into effect at different levels. Established HVM chip fabs must keep sourcing specialty materials regardless of political whims, because our modern world relies on a steady supply of semiconductor devices to maintain our communications, entertainment, health-care, and transportation infrastructures.

Critical Materials Reports™ and Market Briefings: https://techcet.com/shop/

ABOUT TECHCET: TECHCET CA LLC is an advisory services firm focused on process materials supply-chains, electronic materials business, and materials market analysis for the semiconductor, display, solar/PV, and LED industries. Since 2000, the company has been responsible for producing the SEMATECH Critical Material Reports™, covering silicon wafers, semiconductor gases, wet chemicals, CMP consumables, Photoresists, and ALD/CVD Precursors. The Critical Materials Council (CMC) of semiconductor fabricators is a business unit of TECHCET, and includes materials supplier Associate Members. For additional information about reports, market briefings, CMC membership, or custom consulting please contact info(at)cmcfabs.org, +1-480-332-8336, or go to http://www.techcet.com or http://www.cmcfabs.org.

At the 2018 Critical Materials Council (CMC) Seminar, held last October in Ningbo, China in coordination with China's IC Materials Technology Innovation Alliance (ICMtia), representatives of global chip-makers including Intel, GlobalFoundries, and Texas Instruments discussed ways to ensure electronic materials supply-chain robustness in an era of short-sighted protectionist tariffs. All three companies have high-volume manufacturing (HVM) fabs in mainland China along with the US, and all need to source a wide range of specialty materials from global suppliers.

During private face-to-face meetings between CMC fab members in Ningbo, held just after the public CMC Seminar, ON Semiconductor shared that they have a plan prepared to deal with tariffs goings into effect at different levels. Established HVM chip fabs must keep sourcing specialty materials regardless of political whims, because our modern world relies on a steady supply of semiconductor devices to maintain our communications, entertainment, health-care, and transportation infrastructures.

Critical Materials Reports™ and Market Briefings: https://techcet.com/shop/

ABOUT TECHCET: TECHCET CA LLC is an advisory services firm focused on process materials supply-chains, electronic materials business, and materials market analysis for the semiconductor, display, solar/PV, and LED industries. Since 2000, the company has been responsible for producing the SEMATECH Critical Material Reports™, covering silicon wafers, semiconductor gases, wet chemicals, CMP consumables, Photoresists, and ALD/CVD Precursors. The Critical Materials Council (CMC) of semiconductor fabricators is a business unit of TECHCET, and includes materials supplier Associate Members. For additional information about reports, market briefings, CMC membership, or custom consulting please contact info(at)cmcfabs.org, +1-480-332-8336, or go to http://www.techcet.com or http://www.cmcfabs.org.

%20(1).png)